HANDBOOK

OF

# ANALOG COMPUTATION

The publication of this professionally prepared handbook could only be realized at a considerable investment in time and money. To defray some of the publication costs, a nominal charge of \$5.00 per copy is made. Of course, this handbook is supplied free of charge to all Systron-Donner Computer users and to persons who participate in a Systron-Donner Analog Computer Seminar.

To order your copy, please address your request to:

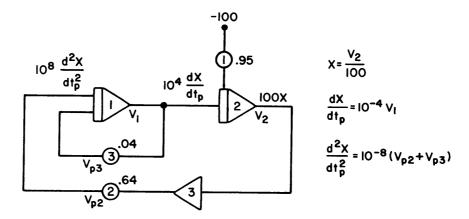

**Analog Computer Operations Group**

SYSTRON-DONNER CORPORATION 888 Galindo Street Concord, California 94520

### HANDBOOK OF

# ANALOG COMPUTATION

(INCLUDING APPLICATION OF DIGITAL CONTROL LOGIC)

### Prepared by

Maxwell C. Gilliland, Ph.D. COMPUTER RESEARCH, INC.

and

Analog Computer Staff

SYSTRON-DONNER CORP.

JUNE 1967

| = |  |  |  |

|---|--|--|--|

|   |  |  |  |

|   |  |  |  |

|   |  |  |  |

|   |  |  |  |

|   |  |  |  |

## **Table of Contents**

| Chapter | Title                                                 |

|---------|-------------------------------------------------------|

| 1       | The Motivation for Analog Computers                   |

| 2       | Basic Analog Computing Elements                       |

| 3       | Elementary Analog Programming                         |

| 4       | Block Programming for Physical Systems                |

| 5       | Scaling                                               |

| 6       | Computer Operation                                    |

| 7       | Logical Algebra                                       |

| 8       | Basic Operation of Digital Logic Elements             |

| 9       | Circuits for Simple Logical Functions                 |

| 10      | Circuits for Simple Linear and Non-Linear Functions   |

| 11      | Simulation of Constant Coefficient Transfer Functions |

| 12      | Control System Simulation                             |

| 13      | Fundamentals of Vector Analysis                       |

| 14      | Partial Differential Equations — Part 1               |

| 15      | Basic Iterative Programming                           |

| 16      | Sampled-Data System Simulation                        |

| 17      | Partial Differential Equations — Part II              |

| 18      | Correlation Analysis                                  |

| 19      | On-Line Data Analysis Programs                        |

| 20      | System Optimization                                   |

| 21      | Medical Applications                                  |

| 22      | A Practical Approach to Adaptive Control              |

|         | APPENDIX                                              |

Glossary of Abbreviations

Uniform Graphics for Simulation

١.

11.

# CHAPTER 1 THE MOTIVATION FOR ANALOG COMPUTERS

Analog Computation, based on the modern electronic analog computer, is of fairly recent date. The first commercially available general purpose electronic analog computers appeared on the market in the 1940's. These early machines were an outgrowth of an emerging electronics technology and a critical need for automatic computing machines that could solve complex dynamic problems. Slide Rule and manual equation solving could no longer be relied upon as a practical approach to seeking engineering solutions. Therefore, analog computers became important tools in the design of aircraft, jet engines, atomic reactors, oil refineries, chemical plants, etc.

Many types of analog computers have evolved over the years. The family has included the mechanical differential analyzer, electromechanical differential analyzer, and most recently, the iterative differential analyzer.

The analog computer has always had several advantages compared to a digital computer. These are primarily speed, more simulation capability per dollar, an ability to integrate, and an excellent man-machine interface.

The mainfeature of the analog computer is that it can integrate time-varying voltages. There is no easy way to differentiate. Consequently a mathematical model of a physical system which is expressed in terms of differential equations cannot be solved with the machine directly. It is necessary to reformulate the mathematical model in terms of integral equations, either implicitly or explicitly.

The analog computer can integrate only with respect to time. Thus, a mathematical model which contains partial integrals (corresponding to partial derivatives) with respect to several variables must be approximated by a set of ordinary integral equations with respect to time. Of course, computer time need not correspond to time in the physical world, although it usually does.

Before 1959 the analog computer was a synchronous machine; all its integrators operated in unison. In 1959 the DYSTAC<sup>1</sup> was introduced. The name was an acronym for 'dynamic storage analog computer'. This machine was the forerunner of the iterative differential

DYSTAC is a registered trademark of CSI.

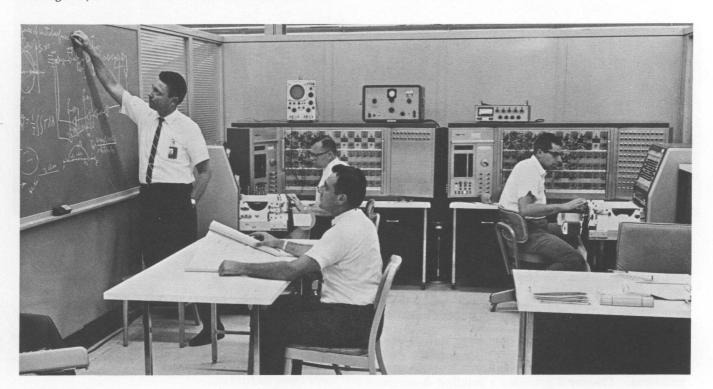

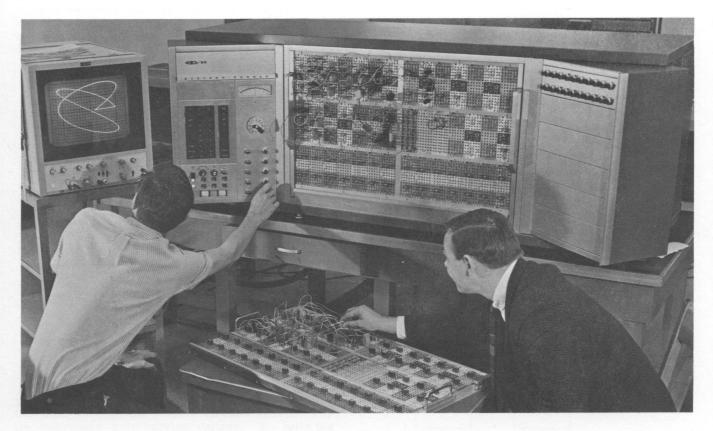

Two large SD 80 computers are used in this engineering laboratory to simulate the behavior of drone helicopters with different load configurations and various automatic flight control systems under a wide range of operating conditions. Simulation saved time and money, reduced the exposure of personnel and material to possible damage when actual flight tests were made, and it also eliminated the necessity of waiting for special environmental (weather) conditions.

(Photo courtesy, Gyrodyne Company of America, Inc.)

Analog computers have long served in the fields of chemistry and process control as a convenient, low cost means to observe, analyze, control, and predict the effect of varying parameters in a dynamic problem. Some of the problems may pertain to enzyme reaction, chemical kinetics, continuous distillation, heat transfer or transport delay -- just to mention a few basic applications of analog computers. The university student shown here is performing a research problem involving the effect of potential barriers on kinetic energy levels.

(Photo courtesy, University of California)

analyzer which appeared in 1960. The iterative differential analyzer is an asynchronous computer; the integrators need not be controlled in unison. They can operate independently either in groups or singly.

In 1962 the analog computer was augmented with digital logic. This innovation first appeared in a machine called the HYDAC. The HYDAC had a very large quantity of synchronous digital logic. Since that time the inclusion of a smaller complement of a synchronous digital logic has become accepted practice.

Digital logic can be used for the implementation of logical decisions. These are based on results obtained from the analog portion of the computer during the solution of the problem. Digital logic also can be used for mode control of the analog computer. All of the Systron-Donner 10/20 and 40/80 series analog computers can be operated in the iterative mode and can be augmented with digital logic.

Analog computers have found widespread acceptance in virtually every area of scientific investigation. This growing interest in analog computers has created a need for complete software, specially designed for the beginner and less experienced user. Also, the recent addition of digital logic control has greatly improved the problem-solving capability of analog computers. How this new feature can be used in analog computation is thoroughly illustrated in this publication.

It is the purpose of this handbook to provide students as well as experienced computer users with comprehensive and up-to-date analog computer software. Chapters 2 to 5 develop the basic fundamentals of computer operation and illustrate the solution of elementary problems. Chapter 6 provides a detailed description of the operating controls and computer logic of the SD 10/20 and 40/80 series computers. This information serves as useful reference material to problem-solutions illustrated in the more advanced discussions

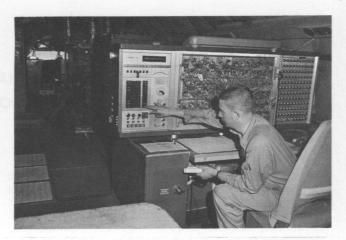

An SD 80 computer mounted inside a Boeing experimental jet transport, selected for the NASA sponsored Supersonic Transport (SST) Program. In this actual in-flight application, the SD 80 is inserted between the pilot's controls and the aerodynamic control surfaces of the jet plane. This permits the total control system to assume the dynamics of any of a wide variety of SST types.

(Photo courtesy, the Boeing Company)

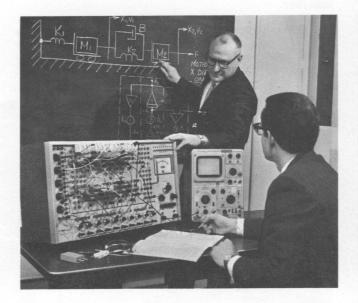

A student in mechanical engineering is shown how to simulate a mass-spring-damper system on an SD 3300 analog computer. Stating equations is unnecessary. Using block programming techniques, illustrated in Chapter 4, the student need only understand the basic relationship of physical variables and constants. Following the program block schematic for a given system, the student can easily program the problem on the computer, observe results on the oscilloscope, and make further parameter adjustments to seek an optimum solution.

which relate iterative programming techniques to the Systron-Donner computers. Chapters 7 to 22 develop more sophisticated programming techniques and applications on a progressive basis.

HYDAC is a registered trademark of EAI.

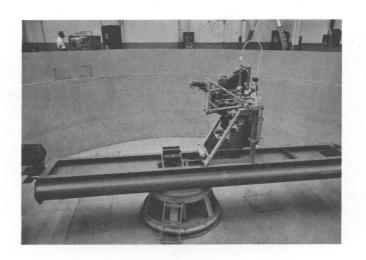

On the Apollo Program, Douglas Aircraft coupled an SD 40 computer to a large centrifuge. The computer calculated and integrated errors in human performance during Apollo lifting body reentry simulation studies. The Systron-Donner computer is seen next to the programmer, in upper left portion of picture.

(Photo courtesy, Douglas Aircraft Co.)

Analog computers are now standard computing equipment for classroom teaching and research work in colleges and universities. Students in the departments of Electrical Engineering, Mechanical Engineering, Chemistry and Biosciences receive instruction in the use of desk top analog computers as basic electronic model builders of dynamic problems. The ease and swiftness of presenting a solution on a readout (oscilloscope, XY recorder), and the ability to vary problem parameters and observe immediately their corresponding effects, have made the analog computer an important teaching aid.

(Photo courtesy, University of Santa Clara)

# CHAPTER 2 BASIC ANALOG COMPUTING ELEMENTS

This chapter shows how electronic equipment and circuits are used to implement mathematical relationships in an analog computer.

# + E -

### OHM'S LAW

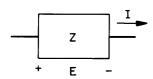

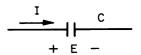

Ohm's law describes the relationship between the current through, and the voltage across a passive impedance. A passive impedance is a collection of passive elements such as resistors and capacitors connected together in an arbitrary way. Such an impedance is generally considered (in analog computing) to be a two-terminal network which can be denoted by

where  $\boldsymbol{Z}$  is the dynamic impedance of the element. Ohm's law states

$$E = ZI$$

for

where I is the time-varying current (in the direction indicated) through the passive element generated by the impressed time-varying voltage, E (with the polarity indicated).

In order to simplify what follows, transform notation will be used where

$$s f(t) = \frac{d}{dt} f(t)$$

and

$$\frac{1}{s} f = \int f(t) dt$$

.

For a resistor Z = R and Ohm's law is

$$E = RI$$

For a capacitor

$$C \frac{dE}{dt} = I$$

so that Ohm's law is

$$E = \frac{1}{Cs} I$$

or

$$E = ZI$$

where

$$Z = \frac{1}{Cs}$$

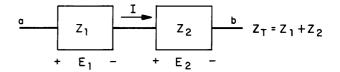

### SERIES and PARALLEL IMPEDANCE

Impedances are additive in series:

This can be proved in a simple way. The total voltage from point a to point b is  $E_T = E_1 + E_2$  and by Ohm's law

$$\mathbf{E}_{\mathbf{T}} \ = \ \mathbf{Z}_{\mathbf{1}} \ \mathbf{I} \ + \ \mathbf{Z}_{\mathbf{2}} \ \mathbf{I} \ = \ (\mathbf{Z}_{\mathbf{1}} \ + \ \mathbf{Z}_{\mathbf{2}}) \ \mathbf{I} \ = \ \mathbf{Z}_{\mathbf{T}} \ \mathbf{I}.$$

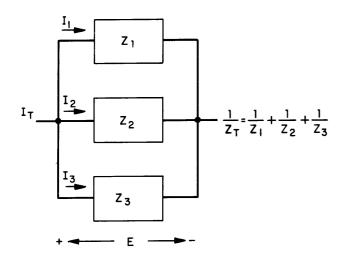

When impedances are connected in parallel the total impedance can be found as the reciprocal of the sum of the reciprocals:

This again can be proved by simple application of Ohm's law:

$$\begin{split} & I_{T} &= I_{1} + I_{2} + I_{3} \\ & I_{T} &= \frac{E}{Z_{1}} + \frac{E}{Z_{2}} + \frac{E}{Z_{3}} \\ & \frac{1}{Z_{T}} = \frac{I_{T}}{E} = \frac{1}{Z_{1}} + \frac{1}{Z_{2}} + \frac{1}{Z_{3}} \,. \end{split}$$

The total impedance of two parallel impedances has the simple formula:

$$Z_{T} = \frac{1}{\frac{1}{Z_{1}} + \frac{1}{Z_{2}}} = \frac{Z_{1}Z_{2}}{Z_{1} + Z_{2}}$$

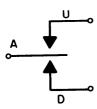

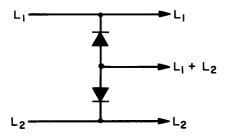

### DIODE

A diode is a non-linear resistor. Its resistance or impedance depends on the direction of the current flowing through it. It is denoted by

where

$$E = ZI$$

$Z = R_1, E > 0$

$= R_2, E < 0$

and generally

$$R_2 \gg R_1$$

.

Typically,  $R_1$  ranges between 1 ohm and 100 ohms; and  $R_2$  between 100,000 ohms (100K  $\!\Omega\!$ ) and 1,000,000 ohms (1M  $\!\Omega\!$ ). Thus the diode is an approximation to a switch for which

$$R_1 = 0$$

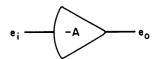

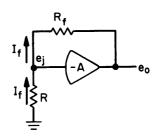

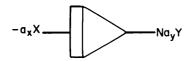

### OPERATIONAL AMPLIFIER

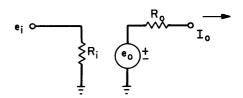

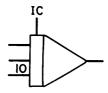

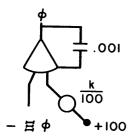

An operational amplifier is of the type that is called a d-c amplifier; it amplifies not only time-varying voltages, but also d-c or constant voltages. It is characterized by its excellent stability and extremely high low-frequency gain (amplification). It is denoted by

where

$$e_0 = -A e_i$$

.

These voltages are measured with respect to ground (zero reference). The gain, A, is usually frequency dependent and will decrease with increasing frequency. As will be seen presently, this becomes a limiting factor in the use of a computer at high speeds. An equivalent circuit for the amplifier is

where, generally,  $R_i$  is greater than  $10^6$  ohms and  $R_0$  less than  $10^{-4}$  ohms (closed-loop) at zero frequency. However, the amplifier is current limited. That is, it will only perform satisfactorily if the output current,  $I_0$ , is less than some value. The current limit for the S-D¹ amplifier is ±25 milliamperes at ±100 volt output. The amplifier is also voltage limited; it will not function satisfactorily if the output voltage,  $e_0$ , is greater, in absolute value, than some upper limit. The limit for the S-D solid-state 100 volt amplifier is 105 volts. Since the output of these amplifiers contains unwanted noise whose magnitude typically can be  $10^{-2}$  volts, their effective useful range is about three and one-half decades ( $5 \times 10^{-2}$  to  $10^2$  volts).

### GENERATION OF TRANSFER FUNCTIONS

In what follows, it will be assumed that the input impedance of the operational amplifier is infinite, the output impedance is zero, and the gain is infinite.

<sup>&</sup>lt;sup>1</sup> Abbreviation for Systron-Donner.

These assumptions introduce negligible error at zero frequency and are a good approximation at mid-frequencies. At high frequency, the assumptions cannot be made (particularly for gain).

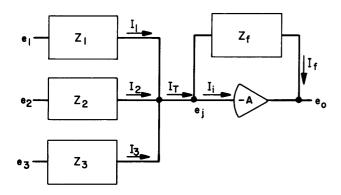

Consider an amplifier with input and feedback (from output to input) impedances and applied input voltages as shown.

From Ohm's law

$$\begin{split} & I_{T} &= \frac{(e_{1} - e_{j})}{Z_{1}} + \frac{(e_{2} - e_{j})}{Z_{2}} + \frac{(e_{3} - e_{j})}{Z_{3}} \\ & I_{f} &= \frac{e_{j} - e_{o}}{Z_{f}} \\ & I_{T} &= I_{f} + I_{j} . \end{split}$$

Now if the input impedance,  $R_i$ , of the amplifier is assumed to be infinite

$$I_i = \frac{e_j}{R_i} = 0$$

for finite e, . Thus

$$I_T = I_f$$

and

$$\frac{(e_1 - e_j)}{Z_1} + \frac{(e_2 - e_j)}{Z_2} + \frac{(e_3 - e_j)}{Z_3} = \frac{e_j - e_o}{Z_f} - - - - (1)$$

Further, if the gain, A, of the amplifier is assumed to be infinite, then

$$e_{j} = \frac{e_{0}}{-A} = 0$$

This is a reasonable assumption at low frequencies since as noted above  $e_0$ , at most, will be in the neighborhood of 100 volts in absolute value. Thus, equation (1) becomes

$$\frac{e_1}{Z_1} + \frac{e_2}{Z_2} + \frac{e_3}{Z_3} = -\frac{e_0}{Z_f}$$

and

$$e_0 = -\left[\frac{Z_f}{Z_1} e_1 + \frac{Z_f}{Z_2} e_2 + \frac{Z_f}{Z_3} e_3\right] . ----(2)$$

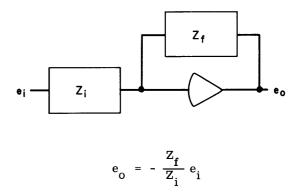

The simplest case is

which can be expressed

$$\frac{e_o}{e_i} = -\frac{Z_f}{Z_i}. \qquad (3)$$

By a suitable choice of impedances many desired transfer functions can be generated. (Henceforth, the units of megohm and microfarad will be used for resistance and capacitance respectively.)

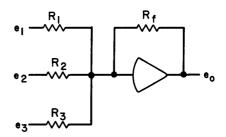

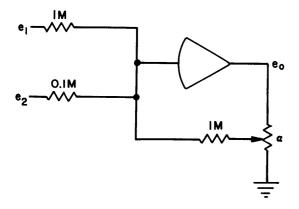

### SUMMER (ADDER)

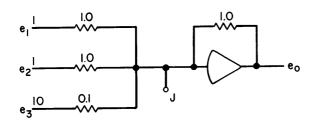

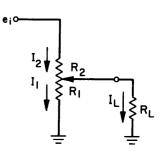

Consider the configuration shown below, which is called a summer.

If, in equation (2), the substitutions

$$Z_1 = R_1$$

$$Z_2 = R_2$$

$$Z_3 = R_3$$

$$Z_f = R_f$$

are made, then

$$e_0 = -\frac{R_f}{R_1} e_1 - \frac{R_f}{R_2} e_2 - \frac{R_f}{R_3} e_3$$

A set of typical values (in megohms) for these resistors in a summer in a computer is

$$R_1 = R_2 = R_f = 1.0$$

$$R_3 = 0.1$$

so that

$$e_0 = -e_1 - e_2 - 10e_3$$

.

In a computer, access is usually provided to the input (summing) junction so that additional input resistors or feedback components can be added to the summer circuit externally. Thus, the summer circuit is

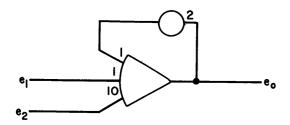

where the gains (multiplying factors) are indicated at each input, and the summing junction terminal by J. The program symbol for the summer is

where the input gains are omitted if they are unity. If it is desired to indicate the junction or summing junction (high-gain input), the symbol becomes

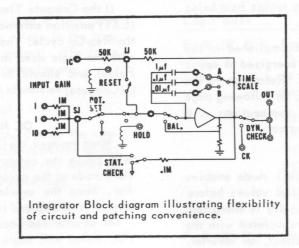

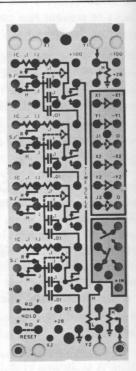

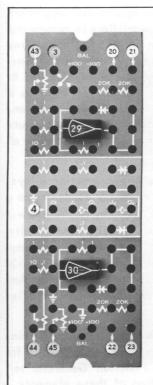

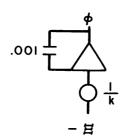

### INTEGRATOR

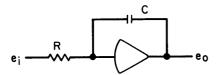

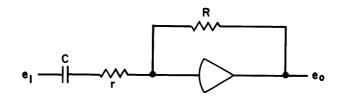

The high-gain input is labeled only if pertinent. Consider the configuration shown below, which is called an integrator

Substitution in equation (3) of

$$Z_i = R, Z_f = \frac{1}{Cs}$$

leads to the transfer function

$$\frac{e_0}{e_i} = -\frac{1}{RCs}$$

or

$$e_0 = -\frac{1}{RCs} e_i = -\frac{1}{RC} \int e_i(t) dt$$

If R=1, C=1, then

$$e_{o} = -\int_{0}^{t} e_{i}(t)dt$$

so that the output voltage,  $e_{\rm Q}$ , of the amplifier will be the integral with respect to time of the time-varying input voltage,  $e_{\rm i}$ .

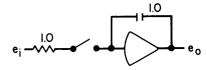

If a switch is included as shown

and if

- 1) there is an initial charge stored on the capacitor which results in the voltage,  $e_0$  (0)

- 2) the switch closes at t=0,

then

$$e_{O} = e_{O}(0) - \int_{O}^{t} e_{i}(t)dt$$

.

It is common practice to call this initial voltage the 'initial condition' for the integrator. The derivation of this terminology is obvious from mathematics.

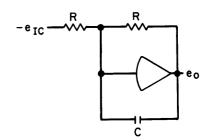

It is necessary to find a practical way to establish the initial condition or initial voltage for the integrator. To accomplish this, the circuit below is used.

Here

$$\frac{1}{Z_f} = Cs + \frac{1}{R} = \frac{RCs + 1}{R}$$

$$Z_f = \frac{R}{RCs + 1}$$

$$Z_z = R$$

and substituting in equation (3)

$$e_{o} = (-\frac{1}{RCs + 1})(-e_{IC}) = \frac{1}{RCs + 1}e_{IC}$$

or

$$RC \frac{de_0}{dt} + e_0 = e_{IC}.$$

The solution of this differential equation is

$$e_o = A \exp(\frac{-t}{RC}) + e_{IC},$$

where A is a constant depending on the initial voltage stored on the capacitor before  $\mathbf{e}_{IC}$  was applied. Then

$$\lim_{t\to\infty} e_0 = e_{IC},$$

For practical cases, it is only necessary that t>10RC, since  $e^{-10}$ <.0001, which is compatible with the accuracy of the circuit. The result in simple terms is: to guarantee the establishment of the initial condition it is necessary to wait 10RC seconds after the voltage,  $-e_{\rm IC}$ , has been applied to the circuit.

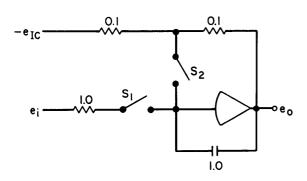

The two previous circuits, combined with appropriate switches as shown below, constitute a practical integrator

The operation is as follows:

With  $S_2$  closed and  $S_1$  open,  $e_0 = e_{IC}$  after 1.0 second (or 0.1 second if C = 0.1, etc.).

With  $S_2$  open,  $e_0$  still equals  $e_{IC}$ , since the current through the capacitor is zero. (This must be true since both  $S_1$  and  $S_2$  are open and the input impedance of the amplifier is assumed to be infinite.)

With  $S_1$  closed at, say, t=0, then

$$e_{O}(t) = e_{IC} - \int_{O}^{t} e_{i}(t)dt$$

If at t = T,  $S_1$  is again opened,  $e_O$  will stop changing and remain at the last value before  $S_1$  opened, namely

$$e_{O}(T) = e_{IC} - \int_{O}^{T} e_{i}(t)dt.$$

If  $S_2$  is closed again while  $S_1$  is open, the output of the integrator will return to

$$e_0 = e_{IC}$$

.

Each integrator in a computer has these switches as part of its circuit. They are open or closed depending on what the programmer wants the integrator to do. The state of these switches is called the integrator mode. If all the integrators are controlled in unison, the switch states are determined by the main computer mode.

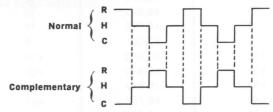

The modes have simple names with obvious interpretations. During the R, or reset (IC) mode, initial voltages are impressed on the integrator capacitors. During the compute or C mode, the integrators integrate input voltages. During the hold or H mode, the integrator outputs remain constant at the last value achieved before entering the hold mode. Thus, the mode permits the programmer to stop the computation at any time, enabling him to evaluate what has happened thus far in the calculation. The table below shows the states of  $S_1$  and  $S_2$  in the various modes. The numeral 1 indicates the switch is closed (logical 1) while 0 indicates the switch is open (logical 0).

| MODE  | $s_1$ | $\mathbf{s_2}$ |

|-------|-------|----------------|

| R(IC) | 0     | 1              |

| H     | 0     | 0              |

| С     | 1     | 0              |

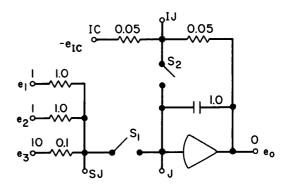

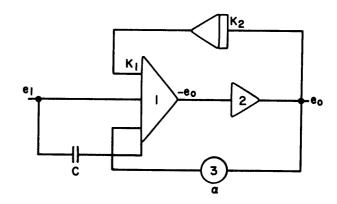

Finally, the general integrator circuit is shown below together with a definition of its transfer function for various modes.

$$-\int_{0}^{T} \left[ e_{1}(t) + e_{2}(t) + 10 e_{3}(t) \right] dt$$

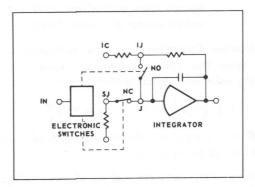

Note that the gain (multiplying factor) of the computing inputs is noted next to the terminals and is determined by the value of the input resistor. The SJ terminal is provided to allow the other external input resistors to be added. The LJ terminal provides the ability to generate an initial condition which is the sum of several voltages. The J terminal permits the connection of additional feedback elements around the amplifier (to be discussed in chapter 10). Also, these terminals provide an external connection for the use of solid-state switches in place of the mechanical switches (relays)  $S_1$  and  $S_2$ . In this case  $S_1$  and  $S_2$  are constrained to be open regardless of integrator mode and the necessary switching is done by the external solid-state switches.

The program symbol for the integrator is

The input gains are usually omitted if they are unity.

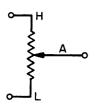

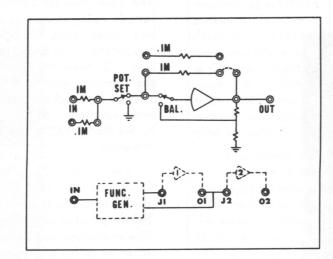

### **POTENTIOMETERS**

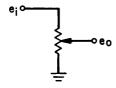

It is necessary to have a device for entering constant parameters in the computer program. This is accomplished with a potentiometer. The circuit for this element is shown below.

If the output voltage,  $e_0$ , of the potentiometer (pot) is applied to an input of another element of the computer, then the input impedance, RL, of the other element is connected from the pot output to ground.

Then

$$I_2 = I_1 + I_L$$

so that

$$\frac{\mathbf{e_i} - \mathbf{e_o}}{\mathbf{R_2}} = \frac{\mathbf{e_o}}{\mathbf{R_1}} + \frac{\mathbf{e_o}}{\mathbf{R_L}}$$

and

$$\frac{\mathbf{e_i}}{\mathbf{R_2}} = \mathbf{e_o} \left[ \frac{1}{\mathbf{R_1}} + \frac{1}{\mathbf{R_L}} + \frac{1}{\mathbf{R_2}} \right].$$

Since

$$R_1 + R_2 = R_t$$

where R<sub>t</sub> = total potentiometer resistance,

$$R_2 = R_t - R_1$$

and

$$e_{o} = \left[\frac{1}{\frac{R_{t}}{R_{L}} + \frac{R_{t}}{R_{L}} - \frac{R_{1}}{R_{L}}}\right] e_{i}$$

$$e_{o} = \left[\frac{R_{1} R_{L}}{R_{t} (R_{L} + R_{1}) - R_{1}} 2\right]$$

$$e_{o} = \alpha e_{i}.$$

Now, obviously, it would be time-consuming to determine  $R_1$ , with the knowledge of  $R_t$ ,  $R_L$  for each new  $\alpha$ . Consequently, in practice, the pot is set with the load connected, by reading the output voltage, e, with a meter, for a known input voltage, which is usually 100 volts.

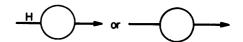

Thus the meter reading is equal to  $100~\alpha$  and the pot is changed until the desired value for  $\alpha$  is obtained. The symbol for the potentiometer is

where H is the notation for the high end, or input. The H is usually omitted since it is obvious from the computer program which side is the input to the pot. The element discussed above is called a two-terminal pot since it has two available terminals (or connections) on the computer program board (patchboard). Sometimes it is desirable to connect the bottom (low) end of the pot to some computing-element instead of ground. In this case the low end is made available at the patchboard. The circuit is

and the program symbol is

where notation for the arm, A, is omitted when it is obvious from the computer program.

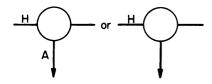

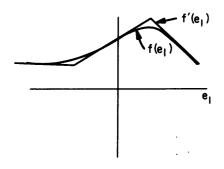

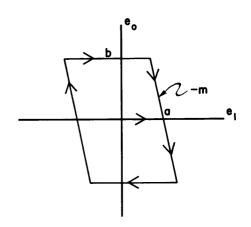

### ARBITRARY FUNCTION GENERATOR

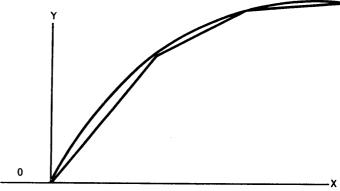

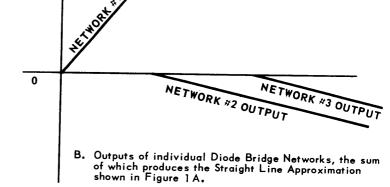

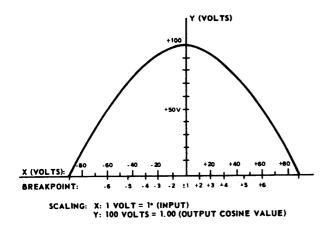

Many mathematical problems to be solved with a computer require the generation of an arbitrary function. This is accomplished with a device called an arbitrary function generator (or frequently, diode function generator, since the internal circuitry uses diodes). This device allows the programmer to approximate the desired function with straight line segments. An example is shown below

Here the function  $f(e_1)$  is approximated by  $f'(e_1)$  with three line segments. In general, each function generator, depending on how it is used, will provide either 10 or 11 line-segments with maximum slope changes of 2 or 2.5:1. Several of these devices can be used together if more segments are required. The location of the slope discontinuity is called the breakpoint and is adjustable. Detailed instructions for the setup of this element appear in Chapter 6.

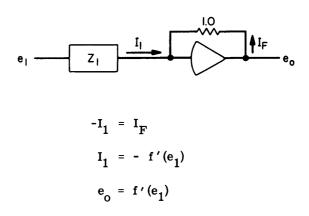

The principle of operation of the function generator depends on the use of a non-linear input impedance for an operational amplifier. That is, the impedance generates an input current proportional to the function which in turn constrains the output voltage to have this functional relationship to the input voltage. A simplified circuit is shown below.

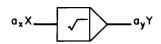

The program symbol for an arbitrary function generator is

### FIXED FUNCTION GENERATOR

Fixed function generators are used to generate oftenused functions such as sine, cosine, log. etc. These are similar to arbitrary function generators in operation, but do not permit the programmer to change the parameters within the device. Generally, a fixed function generator is more accurate and has better frequency and noise specifications than an arbitrary function generator. The program symbol for a sine generator, for example, is

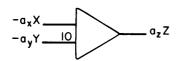

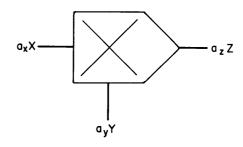

### MULTIPLIER

$$XY = \frac{1}{4} \left[ (X + Y)^2 - (X-Y)^2 \right]$$

The actual equation to be implemented with hardware in order to provide multiplication is

$$e_1 e_2 = \frac{1}{400} \left[ \left| e_1 + e_2 \right|^2 - \left| e_1 - e_2 \right|^2 \right]$$

(4)

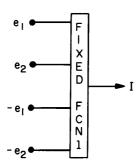

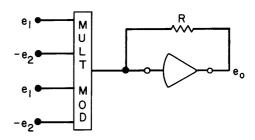

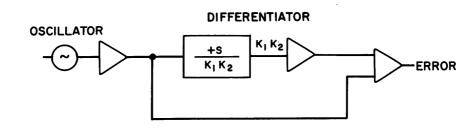

The multiplier module contains two fixed function generators. A block diagram for one of the generators is

(Note that both polarities are required as inputs for both  ${\bf e_1}$  and  ${\bf e_2}.) \,$  The transfer function is

$$I = K \frac{\left| e_1 + e_2 \right|^2}{400}$$

where K is a constant that determines the feedback resistor of the output amplifier (to be shown below).

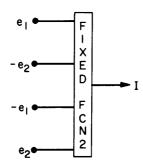

The block diagram for the other is

The transfer function is

$$I = -K \frac{|e_1 - e_2|^2}{400}$$

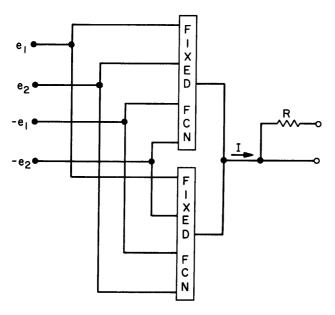

The multiplier module block diagram is

The transfer function is

$$I = \frac{K}{400} \left[ \left| e_1 + e_2 \right|^2 - \left| e_1 - e_2 \right|^2 \right] = K \frac{e_1 e_2}{100}$$

A simplified block diagram for the module is

If the module is connected to an output amplifier

then

$$-\frac{e_0}{R} = \frac{K}{400} \left[ \left| e_1 + e_2 \right|^2 - \left| e_1 - e_2 \right|^2 \right] = K \frac{e_1 e_2}{100}$$

and if

$$K = \frac{1}{R}$$

$$e_0 = \frac{-e_1 e_2}{100}$$

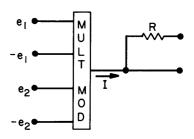

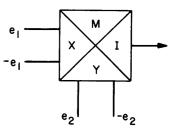

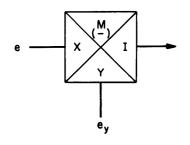

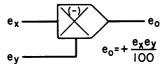

The program symbol for the multiplier module (without the output amplifier) is

With the designations

M: The module is used as a multiplier

I: The output is a current

X, Y: Bipolar inputs

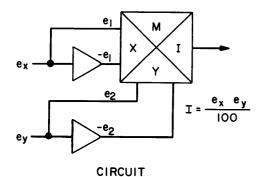

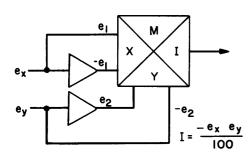

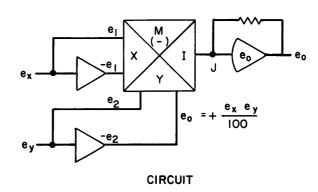

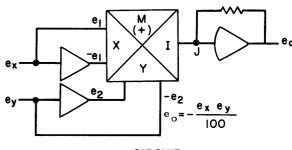

If the bipolar inputs are not naturally available from the program (e.g. other variables) then summers can be used to generate them. This can be done in two ways:

### Case I:

PROGRAM SYMBOL

Note that the "plus sign" associated with the "M" indicates a positive current is generated for a positive product,  $e_x e_y$ . The sign is generally omitted since this is the normal condition.

Case II:

CIRCUIT

PROGRAM SYMBOL

Note that the "minus sign" associated with the "M" indicates a negative current is generated for a positive product.

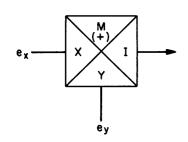

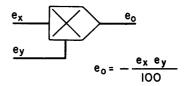

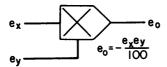

The program symbol for the multiplier module together with an output amplifier is

As before, summers can be used to generate the bipolar inputs if they are not otherwise available.

Case I:

### PROGRAM SYMBOL

(Note that here the sign inversion is due to the output amplifier.)

Case II:

CIRCUIT

PROGRAM SYMBOL

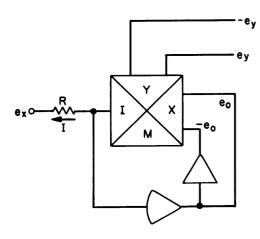

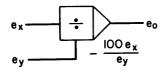

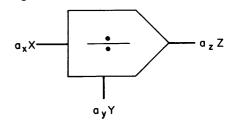

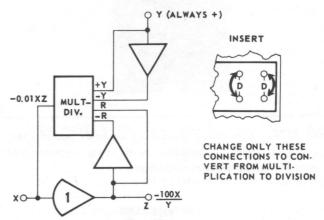

A multiplier module can be used to make a divider with the same output amplifier. (This connection can be made conveniently at the patchboard.)

Here

$$I = K \frac{e_0 e_y}{100} = - \frac{e_x}{R}$$

so that for  $R = \frac{1}{K}$

$$e_{x} = -\frac{e_{0}e_{y}}{100}$$

or

$$e_0 = -\frac{100e_x}{e_y}$$

The programmer's symbol is

From the circuit it can be seen that the condition  $e_y>0$  must hold in order to avoid instability. This is easy to show. The multiplier module can be considered to be a non-linear feedback resister,  $R_f$ . The sign of  $R_f$  is the same as the polarity of  $e_y$ . Suppose in the circuit

$R_f \! < \! 0$ . Then,  $I_f$  will be in the direction shown, for  $e_0 > 0$ , and  $I_f$  will produce an  $e_j < 0$ . Since the gain of the amplifier is negative and large, the circuit will be unstable. An additional restriction,  $|e_{\mathbf{x}}| \leq |e_{\mathbf{y}}|$ , is necessary to ensure that the output amplifier not exceed the voltage limit.

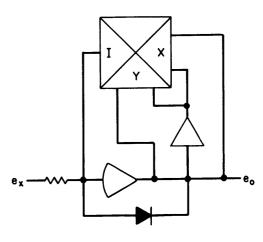

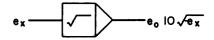

The divider can be used to generate square root in a simple way. If  $e_y = e_0$ ,

CIRCUIT

then

$$e_{O} = -100 \frac{e_{X}}{e_{O}}$$

$\mathbf{or}$

$$e_0^2 = -100 e_x$$

so that

$$e_0 = 10\sqrt{-e_x}$$

,  $e_x < 0$ .

The diode insures that the system will not saturate in the wrong direction if  $\mathbf{e}_{\mathbf{x}}$  goes positive inadvertently.

This circuit has the program symbol

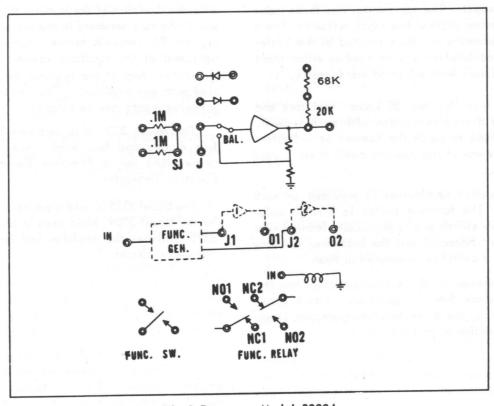

### **FUNCTION SWITCH**

A function switch is a manual switch which can be operated from the control console. It is used to change the computer program during execution. The switch has three positions: up, down, and center (off). Its circuit is shown below.

This is the program symbol as well. The terminals of the switch are located at the patchboard.

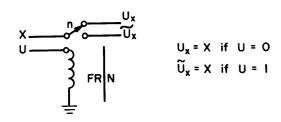

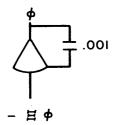

### **FUNCTION RELAY**

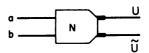

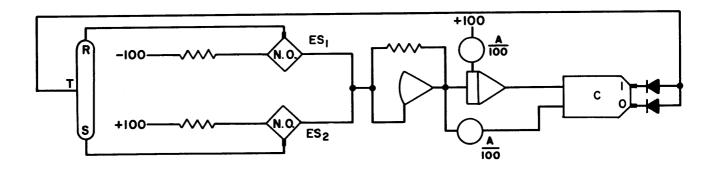

A function relay is used to make program changes automatically during execution. It is energized (logical 1) for an input equal to or greater than +28 volts and is de-energized (logical 0) for an input equal to or less than 0 volts. The circuit is shown below

This is also the program symbol where N is the relay number.

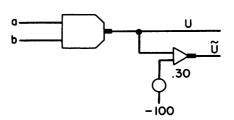

### **ELECTRONIC SWITCH**

An electronic switch is used in much the same way as a function relay; the only restriction being that it must be in series with the junction of an amplifier. Its speed of operation is much greater ( $10^{-5}$  sec) than a function relay ( $10^{-3}$  sec). It requires the same input voltages (logic levels) as the function relay (i.e. logical 1:  $28 \le e_{in} \le 100$ , logical 0:  $-100 \le e_{in} \le 0$ ).

The program symbol is

$$a \xrightarrow{\qquad \qquad \qquad } U_{\alpha}$$

$$U_{\alpha}=a \text{ if } U=I$$

where N is the switch number.

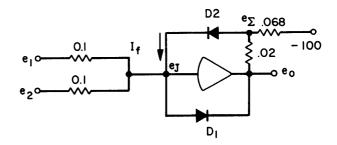

### COMPARATOR

Frequently, it is required to determine the sign of the sum of two variables.

A circuit which accomplishes this is

If  $(e_1 + e_2) > 0$ , then  $e_0$  is limited to approximately 0 volts by  $D_1$  because of its low resistance when it conducts (logical 1). If  $(e_1 + e_2) < 0$ , then  $e_0$  is limited to approximately +28 volts by  $D_2$  (logical 0). The latter is true since

- 1) I<sub>F</sub> must be in the direction shown (e<sub>1</sub> + e<sub>2</sub>>0) and e<sub> $\Sigma$ </sub> > e<sub>J</sub>.

- 2)  $e_0 = 28$  volts since  $e_{\Sigma}$  must be approximately 0 volts due to the high gain of the amplifier.

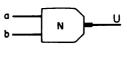

The program symbol for the comparator is

U=1 if (a+b)<0U=0 if (a+b)>0

If both logical comparator outputs are required, then  $\mathbf{e}_0$  is complemented with a biased analog inverter. The program symbol is

and the analog circuit is

### **CHAPTER 3**

### **ELEMENTARY ANALOG PROGRAMMING**

All dependent variables in an analog computer are voltages. Consequently, it is necessary to equate these voltages to physical variables. Since the elements of the computer are voltage limited, scaling will be required. The art of scaling is discussed in Chapter 5. In this chapter scaling is ignored since the necessary concepts can be developed without reference to scaling.

As pointed out in Chapter 1, it is necessary to remember that an analog computer cannot differentiate easily. It is a machine whose main feature is its ability to integrate. Consequently, problems which are defined by differential equations must be reformulated in terms of integral equations either explicitly or implicitly. Consider the problem

$$y = y(x)$$

$$\frac{dy}{dx} + By = 0$$

$$y(0) = A.$$

This can be rewritten as the integral equation

$$y + B \int y dx = 0$$

$$y(0) = A.$$

For this problem computer time will represent x, and

$$y(t) + B \int y dt = 0, t = x$$

$y(0) = A$

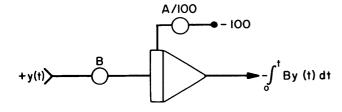

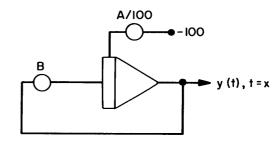

An integrator, as shown in Chapter 2, integrates from t=0 onward. It also requires an initial condition: namely the value of the integral at t=0, which in this case is A. Thus, the problem is formulated for the computer as

$$y(t) = -\int_{0}^{t} By(t)dt,$$

$$y(0) = A$$

(1)

The right half of equation (1) can be generated by

where the constant B and the initial condition A are inserted by means of pots. Remember that the integrator inherently has a sign change. Equation (1) states that y(t) is equal to the negative integral. All that is needed, to complete the computer program for this problem, is to connect the output of the integrator to the input of the pot set to B. Hence, the computer program is

The independent variable, y, can be recorded from the output of the integrator.

In this example the differential equation was reformulated explicitly in terms of an integral equation. It is frequently possible to do this in an implicit way, as the next example will show.

Consider the problem

$$\dot{y} + A\dot{y} + By = f(t), y = y (t)$$

(2)

y(0) = C

$\dot{y}(0) = D$

This is equivalent to

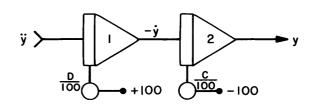

First, y can be generated from ÿ by

(Note that again the pots are used to generate initial conditions.) Using this circuit, the complete program can be generated by

where equation (2) is satisfied by applying the correct inputs to integrator 1.

f(t) A -By B -y

Next, the use of non-linear elements is demonstrated. Consider  $% \left( 1\right) =\left( 1\right) \left( 1\right)$

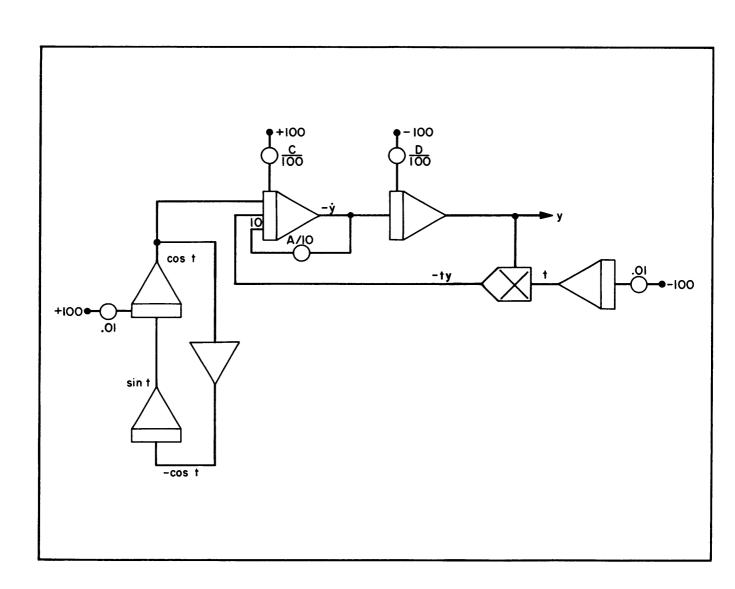

$$\dot{y} + A\dot{y} + ty = \cos t, 1 \le A \le 10,$$

$\dot{y}(0) = C,$

$y(0) = D.$

The computer program (except for scaling) is

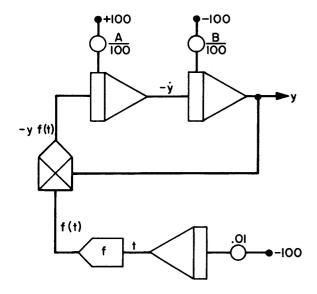

As another example, consider

$$\ddot{y} + f(t)y = 0$$

$$\dot{\mathbf{v}}(0) = \mathbf{A}$$

$$y(0) = B$$

The computer program is

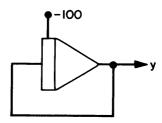

The next example shows how the DCU's (Chapter 8) can be used to determine the solution of a differential equation for a specified value of the independent variable. Suppose it is required to find y (.17) for

$$\dot{\mathbf{y}} + \mathbf{y} = \mathbf{0}$$

$$y(0) = 100.$$

From above, the analog program which generates y is

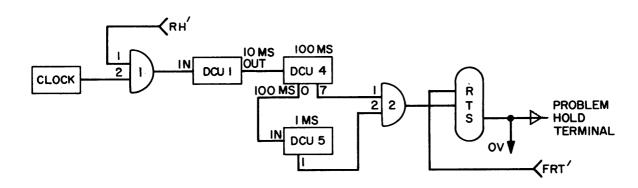

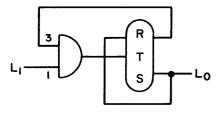

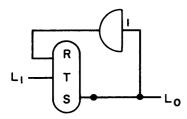

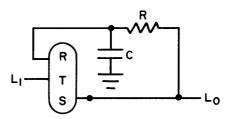

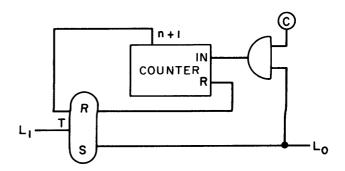

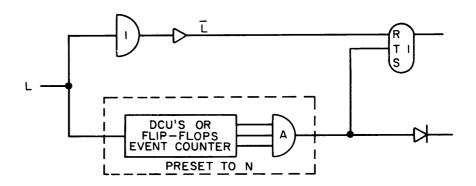

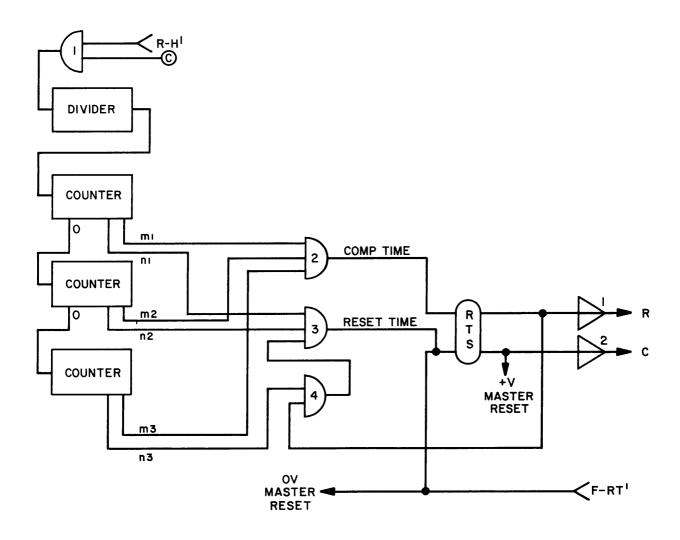

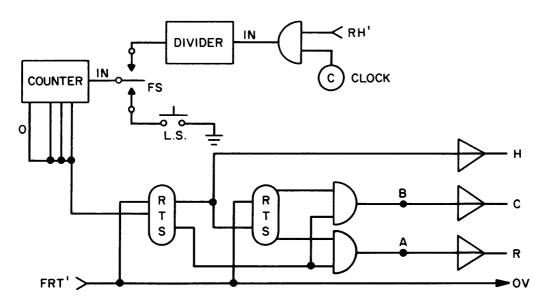

In order to determine y(.17) the computer is allowed to compute for 0.17 seconds and then put into hold. The latter can be accomplished by applying +28 volts to the "problem hold" terminal at the patchboard after 0.17 seconds. This will halt the entire computer and in particular the computation carried out by the above program. The digital program which will do this is shown below:

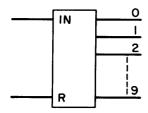

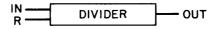

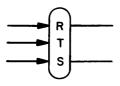

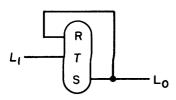

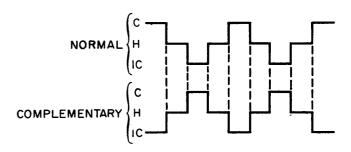

The operation is as follows: The clock pulses are not applied to DCU 1 until the machine is in compute because the output of the RH' bus is a logical 0 in I C and this is an input to gate 1. The FF is initially in the R state when the machine is in compute having been reset by the FRT' Logic output. Divider 1 reduces the clock frequency of 1000 cycles/sec to 100 cycles/sec. The output of the 0 count of counter 4 is 10 cycles/sec and is connected to the input of counter 5. The 7 count output of counter 4 and the 1 count output of counter 5 are connected to gate 2. Thus, whenever t = 0.17 sec the output of gate 2 will change from 0 to 1, which will change the FF to the S state. At this time the computer will go to the hold mode due to the S output of the FF being connected to the problem hold terminal at the patchboard. Also, the clock and counters will be reset because of the logical 1 applied to the OV terminal. As soon as the machine goes to the reset mode the FRT' logic output will cause the FF to return to the R state. Thus, the logic circuit is ready to be used

again as the computer is manually put first in the reset mode and then the compute mode.

### ALGEBRAIC EQUATIONS

The first examples were intended to illustrate the basic approach to programming. The following illustrates a more serious application of the analog computer. Suppose it is desired to solve a set of simultaneous algebraic equations which are expressed in matrix form by

$$\mathbf{AX} = \mathbf{C} \tag{3}$$

where the  $n \times n$  matrix A and the column matrix C are known. For the purpose of illustration it will be assumed that A is of rank 2, although the derivation which follows is perfectly general. Consider

$$\dot{\mathbf{X}} + \mathbf{A}\mathbf{X} = \mathbf{C} \tag{3a}$$

When the system has reached steady-state (assuming there is one)

$$\dot{X} = 0$$

$$AX = C.$$

Thus the solution to equation (3) is obtained from the steady-state solution of equation (3a). The latter can be written

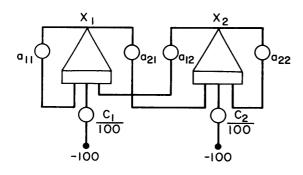

$$\dot{x}_1 + a_{11}x_1 + a_{12}x_2 = C_1$$

$\dot{x}_2 + a_{21}x_1 + a_{22}x_2 = C_2$  (4)

and the analog program is

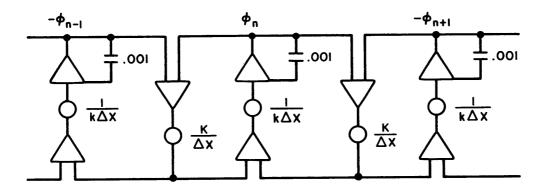

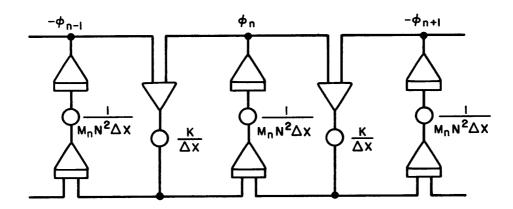

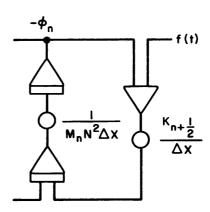

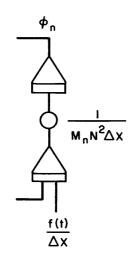

Generally, integrator capacitors are chosen equal to 0.001  $\mu fd$  to decrease the solution time. However, there is no guarantee that the system of differential

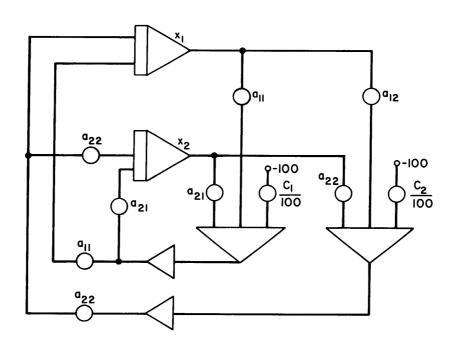

equations, (4), is stable. A different approach will provide an unconditionally stable system of differential equations. If

$$AX = C$$

it follows that

$$A'AX = A'C (5)$$

where A' is the transpose of A. The solution of equation (5) is the same as that for equation (3). Again at steady-state the solution of

$$\dot{X} + A'AX = A'C \tag{6}$$

will be the solution of equation (5) and therefore equation (3). The stability of equation (6) is determined by

$$\dot{X} + A'AX = 0. \tag{7}$$

If equation (7) is multiplied by the row matrix X, then the result is

$$X\dot{X} + XA'AX = 0.$$

It is well known that XA'AX is positive definite (i.e. non-negative for all values of X). Unless X = 0,

$$X\dot{X} < 0$$

and stability is guaranteed. The computer program for equation (6) is

In this program it is easy to change individual coefficients because each pot is associated with only one coefficient. The program can be simplified so that it requires no more equipment than the previous program if the following coefficient changes are made.

This simplified program saves equipment but is inconvenient to use when the solution is required for several different values of the coefficients.

### ARBITRARY CLOSED FUNCTIONS

Many analytic or closed functions can be generated by representing them in terms of their generating differential equations. The following examples illustrate the technique.

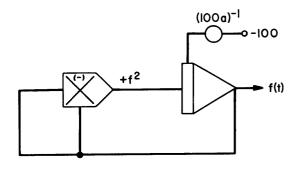

$$f(t) = 1/t, t>a$$

:

This function has the generating equation

$$\frac{\mathrm{df}}{\mathrm{dt}} = -\mathrm{f}^2$$

$$f(a) = \frac{1}{a}.$$

The program which solves the generating equation is

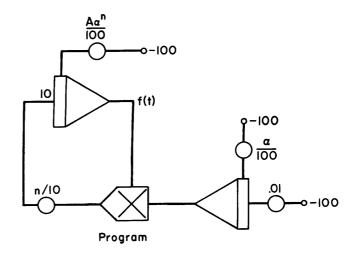

$$f(t) = A(t + \alpha)^{n}, t > 0:$$

$$\frac{df}{dt} = \frac{n}{t + \alpha}f$$

$$f(0) = A\alpha^{n}$$

Generating Equation

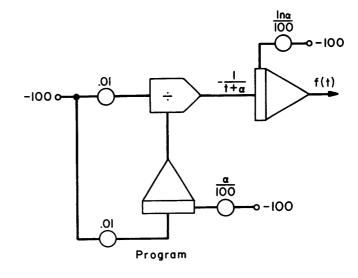

$$f(t) = \ln (t + \alpha), t > 0:$$

$$\frac{df}{dt} = \frac{1}{t + \alpha}$$

$$f(0) = \ln \alpha$$

Generating Equation

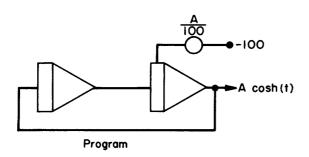

$$f = f$$

$$f(0) = A$$

Generating Equation

### Mean value:

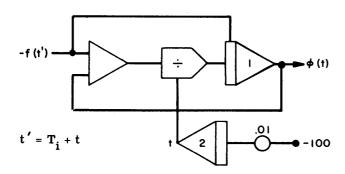

The mean value,  $\phi$  (t), of a function, f (t), over the interval  $\begin{bmatrix} T_1, & T_1 & + & t \end{bmatrix}$  is defined by

$$\phi(t) = \frac{1}{t} \int_{T_1}^{T_1+t} f(\zeta) d\zeta, \ t \ge 0.$$

(8)

The generating equation for  $\phi$  can be obtained by differentiation:

$$\frac{d\phi}{dt} = \frac{1}{t} \left\{ f(T_1 + t) - \phi(t) \right\}$$

(9)

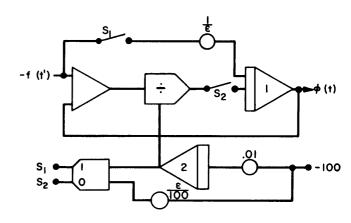

The program is

Suppose the integrators 1, 2 are in the initial condition mode until  $t'=T_1$ , at which time their mode is changed to compute. Then, theoretically, the program will generate the solution of equation (8). However, the program will not work because the right side of equation (9) is indeterminate for t=0. Thus the divider, in the program will have an unstable output. Practical limitations require the Y-input to be at least 3 volts for useful operation. Consequently, it is necessary to choose a different initial condition:

$$\phi(\epsilon) = \frac{1}{\epsilon} \int_{T_1}^{T_1^+ \epsilon} f(\underline{\zeta}) d\zeta,$$

This program is

As before, when  $t'=T_1$ , the mode of integrators 1, 2 is changed from initial condition to compute. Initially S1 is closed and S2 is open. The output of integrator 1 will not be  $\phi$  (t) until  $t=\epsilon$ . When  $t=\epsilon$ , the correct initial condition, namely  $\phi(\epsilon)$ , will have been established for integrator 1. At this time the comparator will be activated, which will open S1 and close S2. Also the output of integrator 2 will be  $\epsilon$ . Thus, the generating equation is implemented by the program starting when  $t=\epsilon^{\gamma}$ . The output of integrator 1 will be  $\phi$  (t),  $t>\epsilon$ .

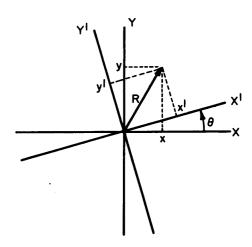

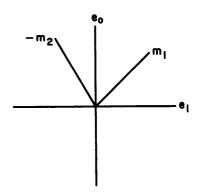

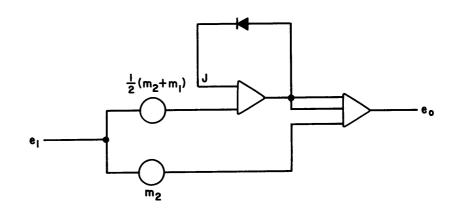

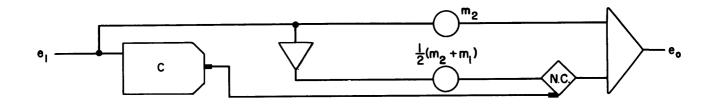

### COORDINATE TRANSFORMATION

Suppose two coordinate systems have the same origin and are displaced by an angular rotation,  $\theta$ :

An X-coordinate point, say x, will have the coordinates

$$x' = x \cos \theta$$

$$y' = -x \sin \theta$$

in the x', y'-coordinate system. Similarly, for a y-coordinate, say y,

$$x' = y \sin \theta$$

$y' = y \cos \theta$ .

Thus, a vector, R, in the X, Y-system with components x, y, will have the components

$$x' = x \cos \theta + y \sin \theta$$

$y' = -x \sin \theta + y \cos \theta$

in the X', Y'-system. In matrix notation

$$R' = TR$$

where R, R' are the representations of the vector in the unprimed and primed coordinate systems respectively, and where

$$\mathbf{T} = \begin{bmatrix} \cos \theta & \sin \theta \\ -\sin \theta & \cos \theta \end{bmatrix}.$$

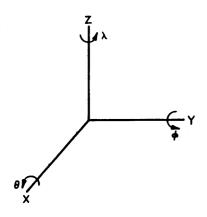

In the three-dimensional coordinate system

positive rotations  $\theta$ ,  $\phi$ ,  $\lambda$  respectively about the X, Y, Z axes correspond to the transformations

$$R_{\theta}^{\mathbf{X}} = \begin{bmatrix} 1 & 0 & 0 \\ 0 & \cos \theta & \sin \theta \\ 0 - \sin \theta & \cos \theta \end{bmatrix}$$

$$R_{\phi}^{\mathbf{Y}} = \begin{bmatrix} \cos \phi & 0 & -\sin \phi \\ 0 & 1 & 0 \\ \sin \phi & 0 & \cos \phi \end{bmatrix}$$

$$R_{\lambda}^{\mathbf{Z}} = \begin{bmatrix} \cos \lambda \sin \lambda & 0 \\ -\sin \lambda & \cos \lambda & 0 \\ 0 & 0 & 1 \end{bmatrix}$$

Any arbitrary three-dimensional rotation can be represented as a product of these three matrices. The superscripts refer to the axis about which the coordinate system is rotated and the subscripts to the name of the angle of rotation.

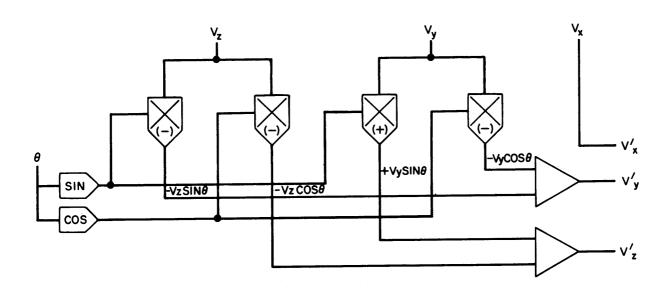

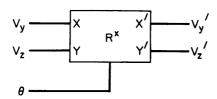

The transformation of a vector, V, by RX is

$$V' = RV$$

$$V'_{x} = V_{x}$$

$$V'_{y} = V_{y} \cos \theta + V_{z} \sin \theta$$

$$V'_{z} = -V_{y} \sin \theta + V_{z} \cos \theta.$$

The program is

Note that  $\theta$  is limited by the range of the sine and cosine function generators.

The program symbol used frequently is

The transformations R<sup>y</sup>, R<sup>z</sup> have similar programs.

### MATRICES

A matrix, A, is a collection of elements:

$$A = \{a_{ij}\}_{j=1,...,m}^{i=1,...,n}$$

(in what follows it is assumed that n = m). Thus, if n = 3

$$\mathbf{A} = \begin{bmatrix} \mathbf{a}_{11} & \mathbf{a}_{12} & \mathbf{a}_{13} \\ \mathbf{a}_{21} & \mathbf{a}_{22} & \mathbf{a}_{23} \\ \mathbf{a}_{31} & \mathbf{a}_{32} & \mathbf{a}_{33} \end{bmatrix}$$

Multiplication by a constant,  $\alpha$ , follows the rule

$$\alpha \mathbf{A} = \alpha \begin{bmatrix} \mathbf{a}_{11} & \mathbf{a}_{12} & \mathbf{a}_{13} \\ \mathbf{a}_{21} & \mathbf{a}_{22} & \mathbf{a}_{23} \\ \mathbf{a}_{31} & \mathbf{a}_{32} & \mathbf{a}_{33} \end{bmatrix} = \begin{bmatrix} \alpha \mathbf{a}_{11} & \alpha \mathbf{a}_{12} & \alpha \mathbf{a}_{13} \\ \alpha \mathbf{a}_{21} & \alpha \mathbf{a}_{22} & \alpha \mathbf{a}_{23} \\ \alpha \mathbf{a}_{31} & \alpha \mathbf{a}_{32} & \alpha \mathbf{a}_{33} \end{bmatrix}$$

which also can be denoted

$$\alpha \mathbf{A} = \alpha \mathbf{a}_{ij}$$

$\alpha \mathbf{A} = \alpha \begin{bmatrix} \mathbf{a}_{ij} \end{bmatrix} = \begin{bmatrix} \alpha \mathbf{a}_{ij} \end{bmatrix}$

when it is understood that the  $a_{ij}$  are the elements of A.

Addition follows the rule

$$A + B = a_{ij} + b_{ij} = (a + b)_{ij}$$

or for, say, n = 2

$$\mathbf{A} + \mathbf{B} = \begin{bmatrix} \mathbf{a}_{11} & \mathbf{a}_{12} \\ \mathbf{a}_{21} & \mathbf{b}_{22} \end{bmatrix} + \begin{bmatrix} \mathbf{b}_{11} & \mathbf{b}_{12} \\ \mathbf{b}_{21} & \mathbf{b}_{22} \end{bmatrix} = \begin{bmatrix} \mathbf{a}_{11} + \mathbf{b}_{11} & \mathbf{a}_{12} + \mathbf{b}_{12} \\ \mathbf{a}_{21} + \mathbf{b}_{21} & \mathbf{a}_{22} + \mathbf{b}_{22} \end{bmatrix}.$$

Multiplication:

$$AB = \sum_{\alpha} a_{i\alpha} b_{\alpha j}$$

Thus for, say, n = 2

$$AB = \begin{bmatrix} a_{11}b_{11} & + & a_{12}b_{21} & & a_{11}b_{12} & + & a_{12}b_{22} \\ a_{21}b_{11} & + & a_{22}b_{21} & & a_{21}b_{12} & + & a_{22}b_{22} \end{bmatrix}.$$

Note that  $AB \neq BA$ . The unit matrix, I, is

$$I = a_{ij} = I, i = j$$

= 0, i \neq j

Thus for, say, n = 3

$$I = \begin{bmatrix} 1 & 0 & 0 \\ 0 & 1 & 0 \\ 0 & 0 & 1 \end{bmatrix}$$

I, has the property

$$IA = AI = A$$

Differentiation:

$$\frac{d}{dx}A = \frac{d}{dx}(a_{ij}) = \frac{da}{dx}ij$$

or for, say, n = 2

$$\frac{d}{dx}A = \frac{d}{dx} \begin{bmatrix} a_{11} & a_{12} \\ a_{21} & a_{22} \end{bmatrix} = \begin{bmatrix} \frac{da_{11}}{dx} & \frac{da_{12}}{dx} \\ \frac{da_{21}}{dx} & \frac{da_{22}}{dx} \end{bmatrix}$$

Transpose: The transpose, A', of A is

$$A' = a_{ii}$$

or for, say, n = 2

$$A' = \begin{bmatrix} a_{11} & a_{21} \\ a_{12} & a_{22} \end{bmatrix}$$

Submatrices: The submatrix,  $S_{ij}$ , corresponding to the element  $a_{ij}$  in A is obtained by deleting the i-th row and j-th column of A. Thus for, say, n=3

$$\mathbf{S_{13}} \ = \begin{bmatrix} \mathbf{a_{11}} & \mathbf{a_{12}} & \mathbf{a_{13}} \\ \mathbf{a_{21}} & \mathbf{a_{22}} & \mathbf{a_{23}} \\ \mathbf{a_{31}} & \mathbf{a_{32}} & \mathbf{a_{33}} \end{bmatrix} = \begin{bmatrix} \mathbf{a_{21}} & \mathbf{a_{22}} \\ \mathbf{a_{31}} & \mathbf{a_{32}} & . \end{bmatrix}$$

Determinant: The determinant, |A|, of A is a scalar quantity and can be found by induction. By definition

$$|A| = \sum_{i=1}^{N} (-1)^{i+j} a_{ij} |S_{ij}|, \text{ for any } i.$$

(10)

(Note that some particular choice is made for i).

For n = 1

$$|A| = a_{11}.$$

Thus, for n = 2,

$$|A| = \sum_{j=1}^{2} (-1)^{1+j} a_{1j} |S_{1j}| = a_{11} S_{11} - a_{12} S_{12}$$

=  $a_{11} a_{22} - a_{12} a_{21}$

or

$$|A| = \sum_{j=1}^{2} (-1)^{2+j} a_{2j} |S_{2j}| = -a_{21} S_{21}^{+} a_{22}^{-} S_{22}^{-}$$

$$= -a_{21} a_{12}^{+} a_{22}^{-} a_{11}^{-}$$

and either calculation leads to the same result. For n = 3,

$$\left|A\right| = \sum_{j=1}^{3} (-1)^{i+j} a_{ij} \left|S_{ij}\right|,$$

and in particular, any of the equations

$$|A| = \sum_{j=1}^{3} (-1)^{1+j} a_{1j} |S_{1j}|$$

$$|A| = \sum_{j=1}^{3} (-1)^{2+j} a_{2j} |S_{2j}|$$

$$|A| = \sum_{j=1}^{3} (-1)^{3+j} a_{3j} |S_{3j}|$$

will lead to the same |A|. If i = 1

$$\begin{array}{rcl} |A| &=& a_{11} s_{11} - a_{12} s_{12} + a_{13} s_{13} \\ &=& a_{11} (a_{22} a_{33} - a_{23} a_{32}) - a_{12} (a_{21} a_{33} - a_{23} a_{31}) \\ &&+& a_{13} (a_{21} a_{32} - a_{22} a_{31}) \\ &=& a_{11} a_{22} a_{33} - a_{11} a_{23} a_{32} - a_{12} a_{21} a_{33} + a_{12} a_{23} a_{31} \\ &&+& a_{13} a_{21} a_{32} - a_{13} a_{22} a_{31} \end{array}$$

Alternatively, |A| can be determined from

$$|A| = \sum_{j=1}^{n} (-1)^{j+j} a_{ij} |S_{ij}|, \text{ for any } j.$$

(11)

A determinant can be multiplied by a constant,  $\alpha$ , in a simple way:

$$|\alpha \mathbf{A}| = \alpha |\mathbf{A}|.$$

From equations (10) and (11) it can be seen that if a matrix B can be generated by m adjacent row interchanges and p adjacent column interchanges starting with matrix A, then

$$|\mathbf{B}| = (-1)^{m+p} |\mathbf{A}|.$$

Cofactor: The cofactor,  $C_{ij}$ , corresponding to the element  $a_{ii}$ , in A is

$$C_{ij} = (-1)^{i+j} |S_{ij}|,$$

or for, say, n = 3

$$C_{13} = \begin{vmatrix} a_{21} & a_{22} \\ a_{31} & a_{32} \end{vmatrix}$$

and

$$C_{23} = - \begin{vmatrix} a_{11} & a_{12} \\ a_{31} & a_{32} \end{vmatrix}.$$

Inverse: The inverse,  $A^{-1}$ , of matrix, A, is

$$A^{-1} = \frac{C_{ji}}{|A|}$$

For example, if n = 2

$$A^{-1} = \frac{1}{a_{11}a_{22}a_{12}a_{21}} \begin{bmatrix} a_{22} & -a_{21} \\ -a_{12} & a_{11} \end{bmatrix}.$$

Orthogonality: A matrix, A, is said to be orthogonal if

$$A' = A^{-1}.$$

Note that R<sup>X</sup>, R<sup>Y</sup>, R<sup>Z</sup> are orthogonal matrices. The geometric interpretation of orthogonality is rotation.

Logical Matrix Operations:

$$(AB)' = B'A'$$

$(AB)^{-1} = B^{-1}A^{-1}$

### DECOMPOSITION OF ORTHOGONAL MATRICES

Frequently the programmer is presented with a composite orthogonal (rotation) matrix which is a function of several angular variables. Usually these angular variables represent successive rotations about coordinate axes. The simplest way to generate the computer program is to decompose the matrix into a product of the RX, RY, RZ matrices and then generate subprograms for each of these matrices. This can be accomplished by following a simple set of rules. These are stated without proof and examples are given. RX, RY, RZ are said to be type 1, 2, 3 matrices respectively. Suppose the composite matrix, M, can be represented

$$\mathbf{M} = \mathbf{A}_1 \mathbf{A}_2 \dots \mathbf{A}_N.$$

The outer matrices are  $\boldsymbol{A}_1,\ \boldsymbol{A}_N$  and the inner matrix  $\boldsymbol{M}_{_T},$  is defined by

$$M_{I} = A_{2}A_{3} \dots A_{N-1}.$$

Now suppose the simplest element (lowest degree homogeneity) of M is located in row i and column j. Then  $A_1$  is of type i and  $A_N$  is of type j. The angular variables corresponding to  $A_1$ ,  $A_N$  will appear in the products of columns j, i respectively. The sense of the rotation,  $A_1$ , (positive or negative) can be found by setting all the variables corresponding to  $A_2$ ...,  $A_N$  equal to zero. The sense of the rotation,  $A_N$ , is similarly found by setting the variables corresponding to A, ...,  $A_{N-1}$  equal to zero. If the simplest element of M is zero, then M has the representation

$$M = A_1 A_2$$

and there is no inner matrix. If the simplest element of M is not zero, then there is an inner matrix and  $M_I$  can be found by setting the variables corresponding to  $A_I$ ,  $A_N$  equal to zero. The further decomposition of  $M_I$  is carried out with the same procedure as for M.

Example:

$$\mathbf{M} = \begin{bmatrix} \cos \Psi & \sin \Psi & 0 \\ -\cos \theta \sin \Psi & \cos \theta \cos \Psi & \sin \theta \\ \sin \theta \sin \Psi & -\sin \theta \cos \Psi & \cos \theta \end{bmatrix}$$

The simplest element is zero and is in row 1 and column 3. Therefore there is no inner matrix and  $A_1$ ,  $A_2$ , are of types 1, 3 respectively. The products of column 3 contain the variable  $\theta$  and the products of row 1 contain the variable for  $\Psi$ . Therefore, the variable for  $A_1$  is  $\theta$  and the variable for  $A_2$  is  $\Psi$ . If  $\Psi$  = 0

$$\mathbf{M} = \begin{bmatrix} 1 & 0 & 0 \\ 0 & \cos \theta & -\sin \theta \\ 0 & -\sin \theta & \cos \theta \end{bmatrix}$$

If  $\theta = 0$

$$\mathbf{M} = \begin{bmatrix} \cos \Psi & \sin \Psi & 0 \\ -\sin \Psi & \cos \Psi & 0 \\ 0 & 0 & 1 \end{bmatrix}$$

Finally,

$$\mathbf{M} = \mathbf{R}_{\alpha}^{\mathbf{X}} \mathbf{R}_{\mathbf{W}}^{\mathbf{Z}}$$

Example:

$$\mathbf{M} \ = \left[ \begin{array}{cccc} \mathbf{Cos} \phi \ \mathbf{Cos} \Psi \ + \ \mathbf{Sin} \theta \ \mathbf{Sin} \phi \\ & -\mathbf{Cos} \theta \ \mathbf{Sin} \ \phi \\ & \mathbf{Cos} \phi \ \mathbf{Sin} \Psi \ \ * \ \mathbf{Sin} \theta \ \mathbf{Sin} \phi \ \mathbf{Cos} \Psi \end{array} \right]$$

The simplest element of M is  $\sin\theta$  and is in row 2 and column 3. The products of column 3 contain the variable  $\Psi$  and those of row 2 the variable  $\phi$ . Therefore  $A_1$ ,  $A_3$  are of types 2, 3 with variables  $\Psi$ ,  $\phi$ , respectively.

If  $\theta = \phi = 0$ , then

$$\mathbf{A}_{1} = \begin{bmatrix} \mathbf{Cos} \ \Psi & \mathbf{0} & -\mathbf{Sin} \ \Psi \\ \mathbf{0} & \mathbf{1} & \mathbf{0} \\ \mathbf{Sin} \ \Psi & \mathbf{0} & \mathbf{Cos} \ \Psi \end{bmatrix}.$$

If  $\Psi = \theta = 0$ , then

$$\mathbf{A_3} = \begin{bmatrix} \cos \phi & \sin \phi & 0 \\ -\sin \phi & \cos \phi & 0 \\ 0 & 0 & 1 \end{bmatrix}.$$

If  $\phi = \Psi = 0$ , then

$$\mathbf{A_2} = \mathbf{M_I} = \begin{bmatrix} 1 & 0 & 0 \\ 0 & \cos \theta & \sin \theta \\ 0 & -\sin \theta & \cos \theta \end{bmatrix}.$$

Finally,

$$\mathbf{M} = \mathbf{R}_{\Psi}^{\mathbf{Y}} \quad \mathbf{R}_{\theta}^{\mathbf{X}} \mathbf{R}_{\phi}^{\mathbf{Z}} .$$

As can be seen from the previous example, it is not necessary to find all the elements of  $A_1$  to determine the sense of  $\Psi$ . Since it is known that  $A_1$  is of type 2 it is only required to evaluate the element in row 1 and column 3 with  $\theta = \phi = 0$ . Similarly, if the element in row 1 and column 2 is found for  $\Psi = \theta = 0$ , then the sense of  $\phi$  is determined.

Example: (Here we use the abbreviations:  $C_{\alpha} = \cos \alpha$ ,  $S_{\alpha} = \sin \alpha$ )

$$\mathbf{M} = \begin{bmatrix} \mathbf{C}_{\phi} \mathbf{C}_{\theta} \mathbf{C}_{\Psi} + \mathbf{C}_{\phi} \mathbf{S}_{\theta} \mathbf{S}_{\lambda} \mathbf{S}_{\Psi} + \mathbf{S}_{\phi} \mathbf{S}_{\theta} \mathbf{C}_{\lambda} \\ \mathbf{C}_{\phi} \mathbf{S}_{\theta} \mathbf{C}_{\Psi} - \mathbf{C}_{\phi} \mathbf{C}_{\theta} \mathbf{S}_{\lambda} \mathbf{S}_{\Psi} - \mathbf{S}_{\phi} \mathbf{C}_{\theta} \mathbf{C}_{\lambda} \\ - \mathbf{C}_{\phi} \mathbf{C}_{\lambda} \mathbf{S}_{\Psi} + \mathbf{S}_{\phi} \mathbf{S}_{\lambda} \end{bmatrix}$$

$$\begin{bmatrix} \mathbf{S}_{\phi}\mathbf{C}_{\theta}\mathbf{C}_{\Psi} + \mathbf{S}_{\phi}\mathbf{S}_{\theta}\mathbf{S}_{\lambda}\mathbf{S}_{\Psi} - \mathbf{C}_{\phi}\mathbf{S}_{\theta}\mathbf{C}_{\lambda} & \mathbf{C}_{\theta}\mathbf{S}_{\Psi} - \mathbf{S}_{\theta}\mathbf{S}_{\lambda}\mathbf{C}_{\Psi} \\ \mathbf{S}_{\phi}\mathbf{S}_{\theta}\mathbf{C}_{\Psi} - \mathbf{S}_{\phi}\mathbf{C}_{\theta}\mathbf{S}_{\lambda}\mathbf{S}_{\Psi} + \mathbf{C}_{\phi}\mathbf{C}_{\theta}\mathbf{C}_{\lambda} & \mathbf{S}_{\theta}\mathbf{S}_{\Psi} + \mathbf{C}_{\theta}\mathbf{S}_{\lambda}\mathbf{C}_{\Psi} \\ & - \mathbf{S}_{\Phi}\mathbf{C}_{\lambda}\mathbf{S}_{\Psi} - \mathbf{C}_{\Phi}\mathbf{S}_{\lambda} & \mathbf{C}_{\lambda}\mathbf{C}_{\Psi} \end{bmatrix}$$

The simplest element of M is  $C_{\lambda}C_{\Psi}$  which is in row 3 and column 3. The products of column 3 contain  $\theta$  and those of row 3 contain  $\phi$ . Thus,  $A_1$  is type 3 and  $A_N$  is also type 3.  $\theta$ ,  $\phi$  are the variables for  $A_1$ ,  $A_N$  respectively. Consider the element in row 1 and column 2. For  $\lambda = \Psi = \phi = 0$  its value is  $\sin\theta$  and consequently

$$A_1 = R_{-\theta}^Z$$

For  $\theta = \lambda = \Psi = 0$  its value is  $\sin \phi$  and consequently

$$A_N = R_{\phi}^Z$$

.

To determine the inner matrix, set  $\theta = \phi = 0$  so that

$$\mathbf{M}_{\mathbf{I}} \begin{bmatrix} & \mathbf{C}_{\Psi} & \mathbf{0} & \mathbf{S}_{\Psi} \\ & -\mathbf{S}_{\lambda}\mathbf{S}_{\Psi} & \mathbf{C}_{\lambda} & \mathbf{S}_{\lambda}\mathbf{C}_{\Psi} \\ & \mathbf{C}_{\lambda}\mathbf{S}_{\Psi} & -\mathbf{S}_{\lambda} & \mathbf{C}_{\lambda}\mathbf{C}_{\Psi} \end{bmatrix}.$$

The simplest element of  $M_I$  is a zero in row 1 and column 2. Also for  $\Psi=0$  the element in row 2 and column 3 is  $Sin\lambda$ . The products of column 2 and row 1 contain the variables  $\lambda$ ,  $\Psi$ , respectively. Thus

$$M_{I} = R_{\lambda}^{X} R_{\Psi}^{Y}$$

.

Finally,

$$\mathbf{A} = \mathbf{R}_{\theta}^{\mathbf{Z}} \mathbf{R}_{\lambda}^{\mathbf{X}} \mathbf{R}_{\Psi}^{\mathbf{Y}} \mathbf{R}_{\phi}^{\mathbf{Z}}.$$

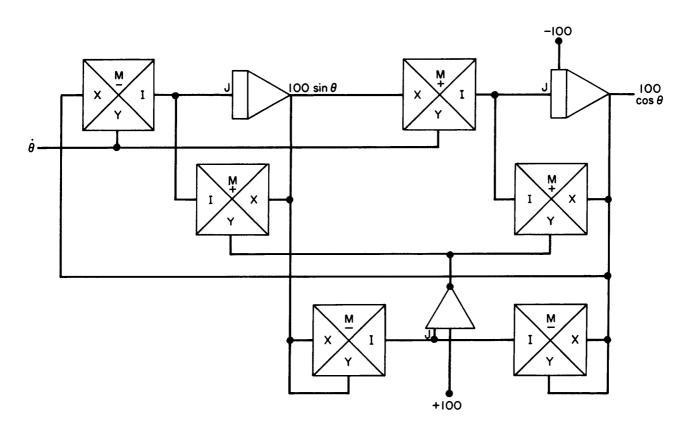

COORDINATE TRANSFORMATIONS WITH UNRESTRICTED ANGLES

The coordinate transformation program is the same as before, except for the use of Sine and Cosine function generators. For unrestricted range we use the variable  $\theta$  and the equations

$$\sin\theta = \int \dot{\theta} \cos\theta \, dt$$

$$\cos\theta = -\int \dot{\theta} \sin\theta dt$$

The program is,

The lower two multipliers and summer generate

$$E = -(100 - \sin^2\theta - \cos^2\theta).$$

This error is used to change the damping of the integrators to ensure orthonormality of  $Sin\theta$ ,  $Cos\theta$ .

### **CHAPTER 4**

### **BLOCK PROGRAMMING FOR PHYSICAL SYSTEMS**

A Valuable Aid to Simulation of Lumped-Parameter Physical Systems

The analog computer, or differential analyzer, is a powerful tool for obtaining dynamic solutions to differential equations. Generally the equations to be solved relate to a physical system of particular interest to the computer programmer, in which case the programmer wishes to simulate his physical system by means of an electrical network whose defining equations are analogous (hence the name analog computer) to the subject physical system. It is desirable then, to arrange the computer mechanization to have a one-to-one correspondence between the problem board and the physical system, so that the programmer "sees" his system rather than an abstract electrical network.

The following discussion will illustrate a method of programming in which the physical elements are treated as blocks rather than as sets of differential equations. Certain useful basic building blocks will be developed, and methods for combining the basic blocks to form any desired physical system (simulation) will be discussed. Simulations generated by the methods to be described will have the advantage that any or all physical parameters appear as single controls in the computer so that any parameter may be changed without affecting any other setting. In addition, any or all variables appear as computer outputs and may be individually monitored.

A lumped-parameter system, by definition, consists of a number of interconnected discrete elements whose individual or collective responses to impressed forces or stimuli are of analytical interest. The forces and responses are related by a mathematical operator. Block programming starts with the selection of basic definition and rules.

### MATHEMATICAL OPERATOR (O)

The operator, or combination of operators, describes the functional relationship between quantities. The most common operators are the following:

### Summer

Constant Multiplier (potentiometer, commonly referred to as "pot")

Inverter - -1 Sign Changer

Integrator -  $\frac{1}{s}$  (La Place Transform Notation)

Differentiator - s (This operator is never used in an analog simulation if it can be avoided, as it usually can).

Variable Multiplier

Arbitrary Function - f(x)

Analytical Function - Trigonometric, Log, Hyperbolic, etc.

Inverse Operator -  $(O)^{-1}$  s,  $\frac{1}{s}$  are inverses

### ELEMENT

The element is the basic unit of the block representation of a system. It has a pair of terminals or nodes, with a value associated with each node. It also has a transference quantity between nodes, or "through" the element which is functionally related by some operator to the node-pair value. The transference quantity may also be referred to as the branch transference or transmission.

The elements required to depict the passive lumpedparameters of most physical systems are very few in number. In particular, five basic elements will suffice for many linear electrical, mechanical, and thermal systems. These are the Summer, Constant Multiplier, Sign Changer, Integrator, and Differentiator.

### BLOCK

A block is the computer mechanization related to a physical element. The input/output variables of a computer block are voltages and currents, but the operator relationship is the same as the simulated element.

Table I gives examples of single elements and their corresponding blocks. Table II gives a few commonly occurring two-element combinations. Combinations of more than two elements can be generated as shown in the following examples. Useful tables of more complicated blocks or transfer-function simulations appear in many publications. 1

### DRIVING SOURCE

A driving source is a source of energy or power for a network of elements.

### SYSTEM STABILITY

A stable system is one whose responses are bounded (finite amplitude limit) for any finite input. An unstable system is one whose responses are not bounded.

### NETWORK

A network is an interconnected set of elements and sources. Elements may be joined together at their nodes, providing the connected nodes have common dimensions and value, and provided the transference quantities have common dimensions.

This discussion concerns elements and networks in which the following two rules apply: (Kirchoff's laws)

- 1. The algebraic sum of the node values around any closed path (loop) in a network is zero.

- 2. The algebraic sum of the transmission quantities at any node is zero.

<sup>1</sup> Korn and Huskey, "Computer Handbook", Chapter 2, McGraw-Hill, New York, 1962.

TABLE I. Single-element Computing Blocks

| PHYSICAL<br>ELEMENT | SCHEMATIC<br>SYMBOL                                                   | MATHEMATICAL<br>RELATIONSHIP                            | PROGRAM BLOCK    |

|---------------------|-----------------------------------------------------------------------|---------------------------------------------------------|------------------|

|                     |                                                                       | Summer 5<br>Y = - (X <sub>1</sub> + X <sub>2</sub> )    | X <sub>1</sub> Y |

|                     |                                                                       | Constant<br>Multiplier<br>(POT)<br>Y = KX               | x(K)             |

|                     |                                                                       | Inverter<br>Y = -X                                      | x————            |

|                     |                                                                       | Integrator $Y = \frac{X}{s}$                            | х——              |

|                     |                                                                       | Differentiator<br>Y = sX                                | X S Y  X Y       |

| Resistor            | E <sub>1</sub> ——R—E <sub>2</sub>                                     | $I = \frac{(E_1 - E_2)}{R}$                             |                  |

| Linear<br>Spring    | x <sub>1</sub>                                                        | $\mathbf{F} = \mathbf{K} (\mathbf{X}_1 - \mathbf{X}_2)$ |                  |

| Torsional<br>Spring | $\theta_1$ $\xrightarrow{F}$ $\overset{K}{\longleftarrow}$ $\theta_2$ | $\mathbf{F} = \mathbf{K} (\theta_1 - \theta_2)$         | -X <sub>2</sub>  |

| Heat<br>Conductor   | T <sub>1</sub>                                                        | $\dot{Q} = K(T_1 - T_2)$                                |                  |

| Viscous<br>Damper   | V₁ — B V2 F                                                           | $F = B(v_1 - v_2)$                                      |                  |

| PHYSICAL<br>ELEMENT     | SCHEMATIC<br>SYMBOL                                 | MATHEMATICAL<br>RELATIONSHIP                                              | PROGRAM BLOCK                                       |

|-------------------------|-----------------------------------------------------|---------------------------------------------------------------------------|-----------------------------------------------------|

| Electrical<br>Capacitor | E <sub>1</sub> ——    C                              | $(\mathbf{E}_1 - \mathbf{E}_2) = \frac{\mathbf{I}}{\mathbf{sC}}$          | Y ——(X <sub>1</sub> -X <sub>2</sub> )               |

| Viscous<br>Damper       | X <sub>1</sub> ——B—X <sub>2</sub>                   | $(\mathbf{X}_1 - \mathbf{X}_2) = \frac{\mathbf{F}}{\mathbf{s}\mathbf{B}}$ |                                                     |

| Mechanical<br>Mass      | V <sub>1</sub> — V <sub>2</sub>                     | $(\mathbf{v_1} - \mathbf{v_2}) = \frac{\mathbf{F}}{\mathbf{s}\mathbf{M}}$ | X <sub>1</sub>                                      |

| Thermal<br>Mass         | T <sub>1</sub>                                      | $(T_1 - T_2) = \frac{\dot{Q}}{sM_T}$                                      | -x <sub>2</sub> s                                   |

| Electrical<br>Inductor  | E <sub>1</sub> E <sub>2</sub>                       | $I = \frac{(E_1 - E_2)}{sL}$                                              | X <sub>1</sub> ———————————————————————————————————— |

| Mechanical<br>Mass      | V <sub>1</sub> ———————————————————————————————————— | $X = \frac{(v_1 - v_2)}{s}$                                               | Y(X <sub>1</sub> -X <sub>2</sub> )                  |

# COMPUTER PROGRAM MECHANIZATION COMMENTS

- 1. Operational amplifiers operate with the junction at virtually zero potential; the currents into the junction through all the input and feedback paths must sum to zero; and there is a sign inversion between the amplifier input and output quantities.

- Any closed-loop in a problem mechanization simulating a stable physical system will generally have an <u>odd</u> number of sign inversions.

- In mechanizing an equation, set the highest order derivative only on the left of the equals sign to obviate the necessity for differentiation.

- 4. The mechanization is accomplished by:

- a) assigning a position in the mechanization diagram to all necessary variables and operators.

- accomplishing the necessary interconnections so that each output has its proper inputs.

- c) checking to see that all input/output relationships in the mechanization are satisfied.

# EXAMPLES OF NETWORK PROGRAMMING

The following examples illustrate some of the techniques used in applying the block programming methods. Examples are given for linear elements only. Non-linearities can be included simply by replacing the potentiometer corresponding to the non-linear element with a multiplier, function generator, or other suitable computing element. Backlash, hysteresis, stiction, etc can be included as required.

TABLE II. Two-Element Computing Blocks

| SCHEMATIC                                           | MATHEMATICAL<br>RELATIONSHIP                                                                              | PROGRAM BLOCK           |

|-----------------------------------------------------|-----------------------------------------------------------------------------------------------------------|-------------------------|

| X <sub>1</sub>                                      | $(X_1 - X_2) = \frac{Y - K (X_1 - X_2)}{a \cdot s}$                                                       |                         |

| $E_1$ $E_2$ $E_2$                                   | $(E_1 - E_2) = \frac{I - \frac{1}{R}(E_1 - E_2)}{sC}$                                                     | (a)                     |

| X <sub>1</sub> ———————————————————————————————————— | $(X_1 - X_2) = \frac{F - K (E_1 - E_2)}{sB}$                                                              | Y                       |

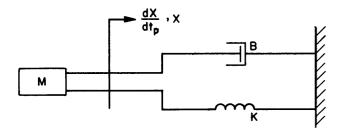

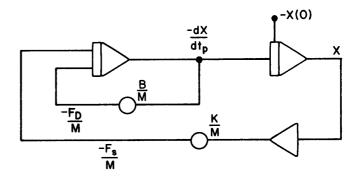

| v <sub>1</sub> ———v <sub>2</sub> ———F               | $(v_1 - v_2) = \frac{F - B (v_1 - v_2)}{sM}$                                                              |                         |

| X <sub>1</sub>                                      | $Y = \frac{(X_1 - X_2) - KY}{a \cdot s}$                                                                  | ( <u>K</u> )            |

| $E_1$ $R$ $E_2$                                     | $I = \frac{(E_1 - E_2) - RI}{sL}$                                                                         | x <sub>1</sub> 1 0 - y  |

| v <sub>1</sub> Bv <sub>2</sub>                      | $\mathbf{F} = \frac{(\mathbf{v_1} - \mathbf{v_2}) - \frac{\mathbf{F}}{\mathbf{B}}}{\mathbf{s}\mathbf{M}}$ | -X <sub>2</sub> - (1/9) |

| X <sub>1</sub>                                      | $Y = \frac{(X_1 - X_2) - \frac{Y}{a \cdot s}}{bs}$                                                        |                         |

| E <sub>1</sub> ——  C———E <sub>2</sub>               | $I = \frac{(E_1 - E_2) - \frac{I}{sC}}{sL}$                                                               | X <sub>1</sub>          |

| F <sub>1</sub> ———————————————————————————————————— | $v = \frac{(F_1 - F_2) - \frac{Kv}{s}}{sM}$                                                               | -^2(p)                  |

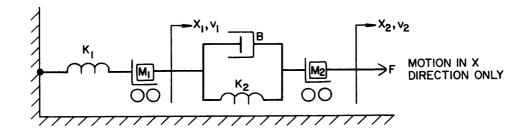

## Element - force equations

Spring

$$K_1$$

:  $F_{s1} = K_1 (X_1 - 0)$

Spring

$$K_2$$

:  $F_{s2} = K_2 (X_2 - X_1)$

Damper B:

$$F_D = B(v_2 - v_1)$$

Initial values at t = 0.

$$X_1 (0), X_2 (0), v_1 (0), v_2 (0)$$

# Forces acting on masses

$$F_{M1} = -F_{s1} + F_{s2} + F_{D}$$

$$F_{M2} = -F_{s2} - F_D + F$$

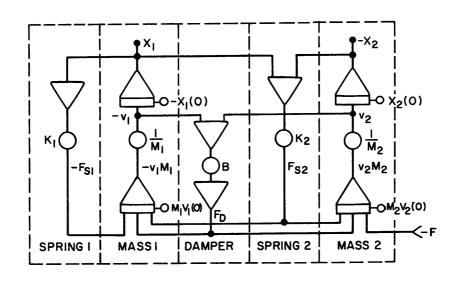

# Steps to mechanize

- 1. Assume  $\mathbf{X_1}$ ,  $-\mathbf{X_2}$ ,  $-\mathbf{v_1}$ ,  $\mathbf{v_2}$  and  $\mathbf{F}$  are available

- 2. Draw blocks for  $\mathbf{M_1}$ ,  $\mathbf{M_2}$

- 3. Draw blocks for  $K_1$ ,  $K_2$ , B

- 4. Make input connections to mass blocks to produce  $\mathbf{X}_1$ ,  $-\mathbf{X}_2$ ,  $-\mathbf{v}_1$ ,  $\mathbf{v}_2$

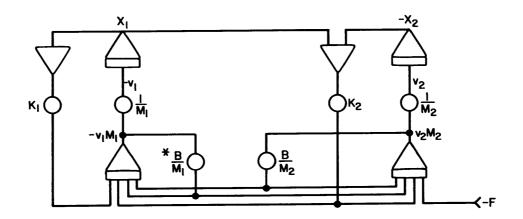

The above mechanization makes each parameter available as an individual adjustment. The programming is easily accomplished by generating the forces imposed on the elements and then operating on the forces to obtain velocity and displacement. Any or all of the initial conditions,  $X_1(0)$ ,  $X_2(0)$ ,  $v_1(0)$  and  $v_2(0)$ , may be zero, or may also be variable.

Note that the block representing the damper contains

two summers. The first summer produces  $(v_1 - v_2)$ , and the second summer acts only as a sign changer. The two-amplifier, one-pot combination can be reduced to a more simple two-pot combination by connecting  $v_1$  and  $v_2$  through B pots to the mass block inputs. The less complex alternate is shown below. This configuration requires fewer amplifiers, but variations in  $M_1$ ,  $M_2$ , or B necessitate two or three adjustments.

\* Do not connect to  $-v_1$  to get pot setting of B instead of  $\frac{B}{M_1}$ . A coefficient pot output cannot be connected

to another coefficient pot input. This is a practical limitation of the computer hardware.

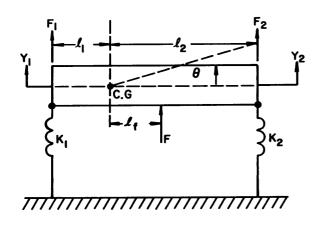

Rigid Bar Supported on Springs

Rigid bar of mass M, moment of inertia about C.G. of I. Assume  $\theta$  small such that  $\theta \approx \sin \theta$ . Vertical motion only.  $Y_0$  is displacement of C.G.

$$\dot{\theta} = \frac{F_2 \ell_2 - F_1 \ell_1 + F \ell_F}{sI} \qquad \dot{Y}_0 = \frac{F_1 + F_2 + F}{sM}$$

$$F_1 = -K_1 Y_1 \qquad Y_1 = Y_0 - \ell_1 \theta$$

$$F_2 = -K_2 Y_2 \qquad Y_2 = Y_0 + \ell_2 \theta$$

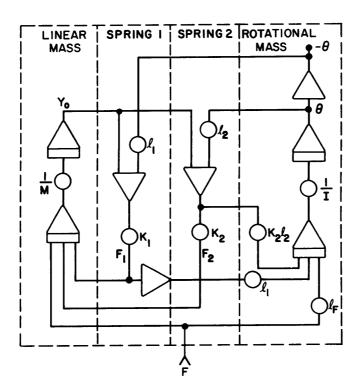

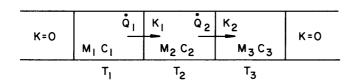

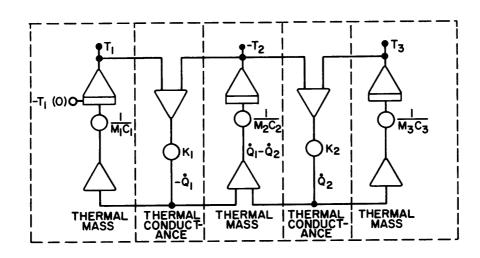

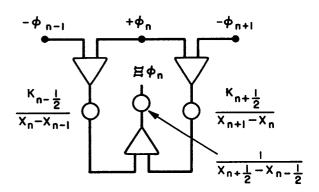

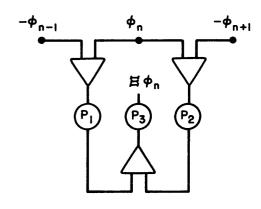

## One-Dimensional Heat Transfer

K-THERMAL CONDUCTIVITY

M-MASS

C-SPECIFIC HEAT

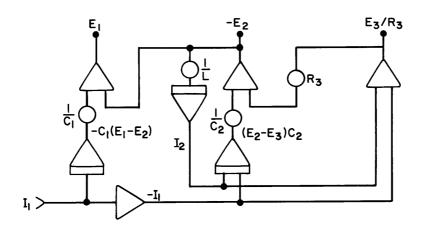

$$\dot{Q}_{1} = K_{1} (T_{1} - T_{2}) \qquad \dot{Q}_{2} = K_{2} (T_{2} - T_{3})$$

$$sT_{1} = \frac{\dot{Q}_{1}}{M_{1}^{c}_{1}} \qquad sT_{2} = \frac{\dot{Q}_{1} - \dot{Q}_{2}}{M_{2}^{c}_{2}} \qquad sT_{3} = \frac{\dot{Q}_{2}}{M_{3}^{c}_{3}}$$

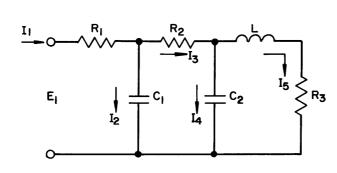

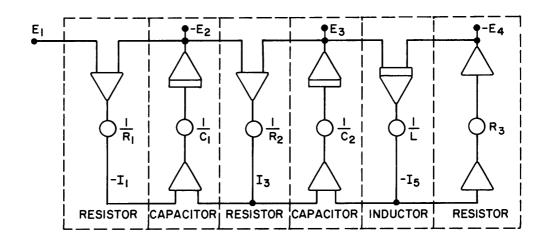

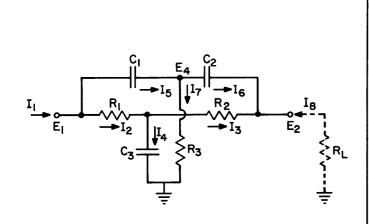

$$I_{1} = \frac{E_{1} - E_{2}}{R_{1}}$$

$I_{2} = I_{1} - I_{3}$

$$I_{3} = \frac{E_{2} - E_{3}}{R_{2}}$$

$I_{4} = I_{3} - I_{5}$

$$I_{5} = \frac{E_{3} - E_{4}}{sL}$$

$E_{2} = \frac{I_{2}}{sC_{1}}$

$E_4 = I_5 R_3$   $E_3 = \frac{I_4}{sC_2}$

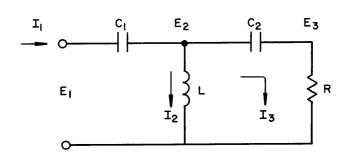

$$E_1 - E_2 = \frac{I_1}{sC_1}$$

$E_2 - E_3 = \frac{I_3}{sC_2}$   $E_3 = I_3 R_3$   $I_2 = \frac{E_2}{sL}$   $I_3 = I_1 - I_2$

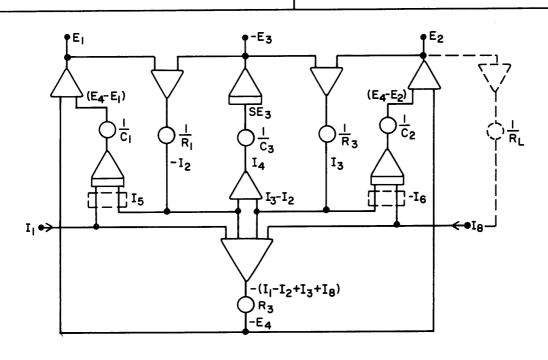

### TWIN-T NETWORK

$$I_{2} = \frac{E_{1} - E_{3}}{R_{1}}; -E_{3} = \frac{I_{3} - I_{2}}{sC_{3}}$$

$$-I_{3} = \frac{E_{2} - E_{3}}{R_{2}}$$

$$(E_{4} - E_{2}) = \frac{-(I_{8} + I_{3})}{sC_{2}}$$

$$(E_{1} - E_{4}) = \frac{I_{1} - I_{2}}{sC_{1}}$$

$$E_{4} = (I_{1} - I_{2} + I_{3} + I_{8}) R_{3}$$

$$E_{1} = (E_{1} - E_{4}) + E_{4}; E_{2} = E_{4} - (E_{4} - E_{2})$$

| 1                                          |  |  |  |  |

|--------------------------------------------|--|--|--|--|

| <i>†</i>                                   |  |  |  |  |

| • *<br>• • • • • • • • • • • • • • • • • • |  |  |  |  |

|                                            |  |  |  |  |

|                                            |  |  |  |  |

| :                                          |  |  |  |  |

|                                            |  |  |  |  |

| 1                                          |  |  |  |  |

|                                            |  |  |  |  |

|                                            |  |  |  |  |

| <u>.</u>                                   |  |  |  |  |

|                                            |  |  |  |  |

|                                            |  |  |  |  |

|                                            |  |  |  |  |

|                                            |  |  |  |  |

| 4<br>15<br>15                              |  |  |  |  |

|                                            |  |  |  |  |

|                                            |  |  |  |  |

|                                            |  |  |  |  |

|                                            |  |  |  |  |

|                                            |  |  |  |  |

|                                            |  |  |  |  |

|                                            |  |  |  |  |

|                                            |  |  |  |  |

|                                            |  |  |  |  |

|                                            |  |  |  |  |

|                                            |  |  |  |  |

|                                            |  |  |  |  |

|                                            |  |  |  |  |

|                                            |  |  |  |  |

|                                            |  |  |  |  |

|                                            |  |  |  |  |

|                                            |  |  |  |  |

|                                            |  |  |  |  |

|                                            |  |  |  |  |

|                                            |  |  |  |  |

|                                            |  |  |  |  |

|                                            |  |  |  |  |

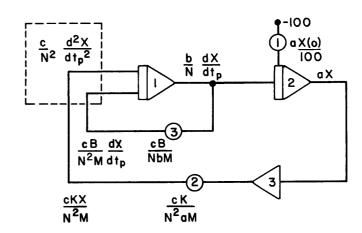

# CHAPTER 5 SCALING

The analog computer is voltage limited to a practical range of operation of  $\pm 100$  volts as a maximum and  $\pm 1$  volt or zero as a minimum. It is usually not possible to numerically equate analog voltages to physical variables. That is, the magnitude of physical variables must be scaled to fall within the useful range of the machine. This procedure is called amplitude scaling.

The analog computer is also limited as to the speed with which it will solve a problem. Practical bounds on solution time are 100 seconds as a maximum and 100 milliseconds as a minimum. Events in the physical world usually occur in time intervals which fall outside these limits. Thus, the simulation of real world phenomena with the analog computer is ordinarily faster or slower. The procedure for relating computer time to physical time is called time scaling.

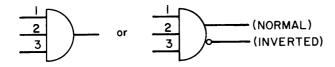

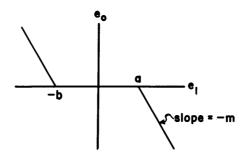

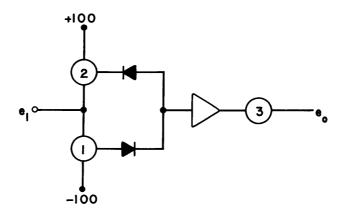

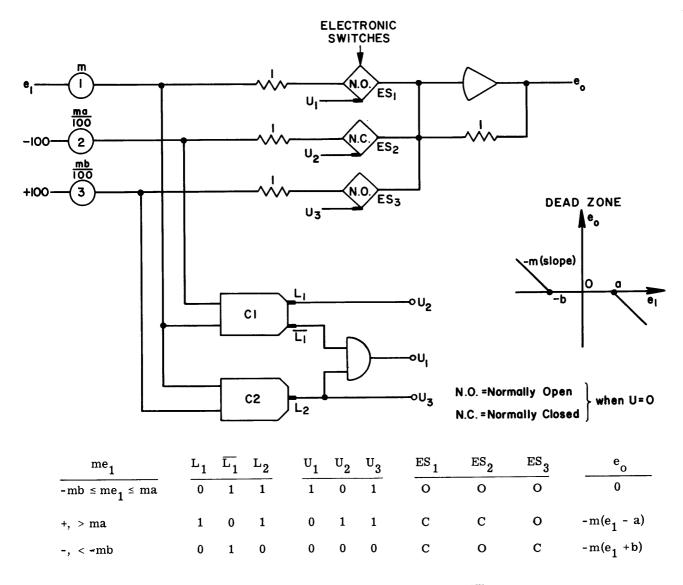

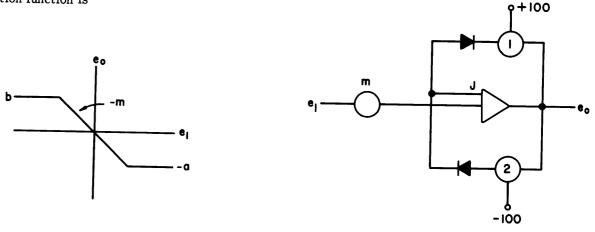

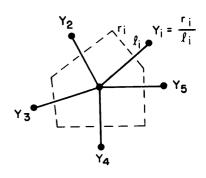

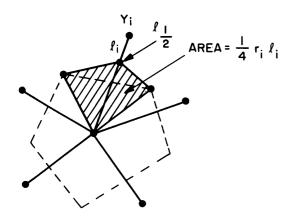

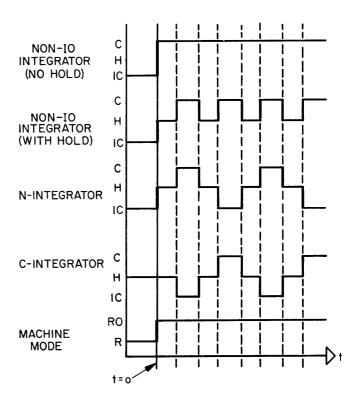

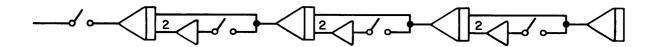

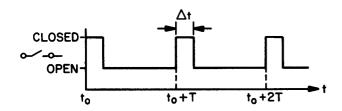

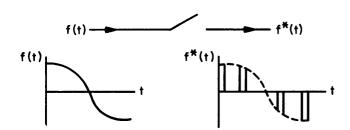

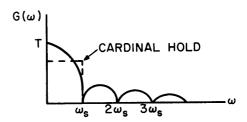

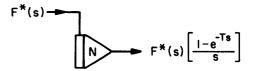

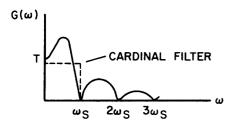

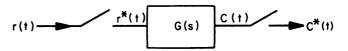

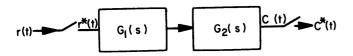

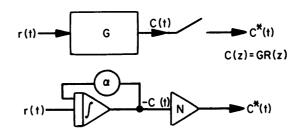

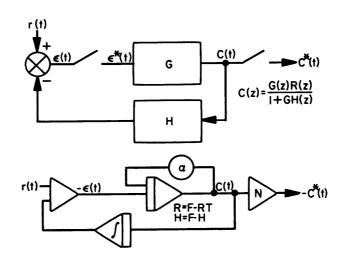

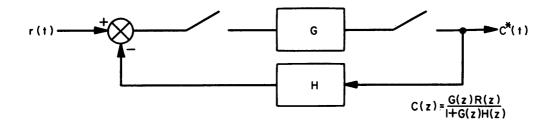

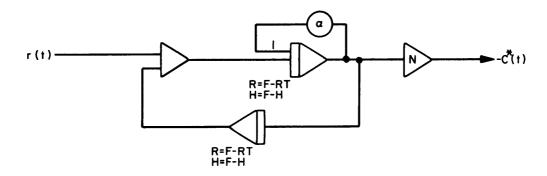

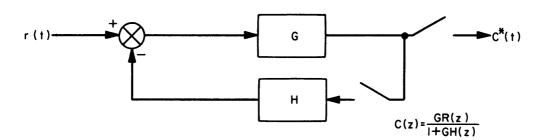

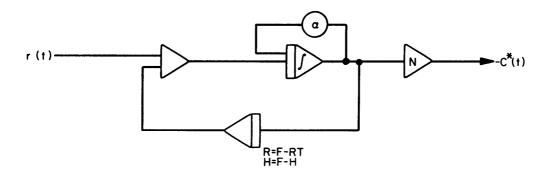

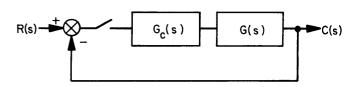

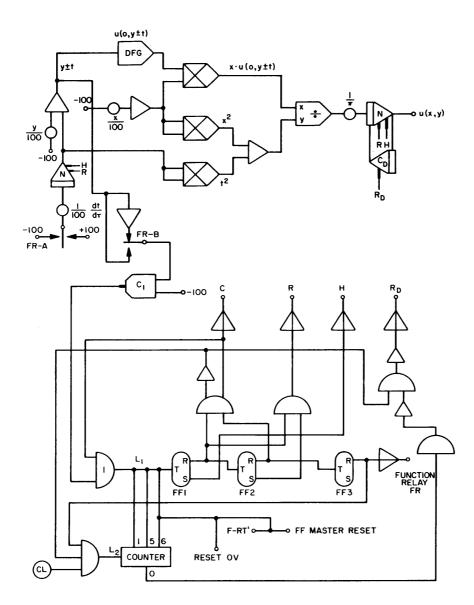

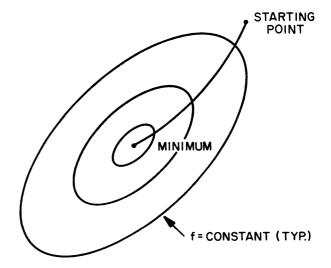

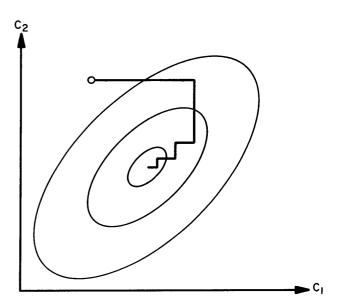

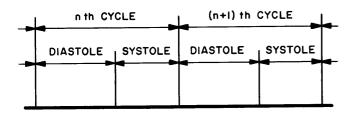

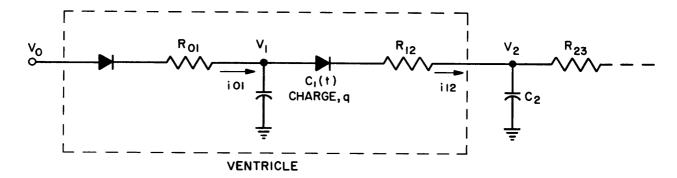

Correct scaling is an important factor in reducing simulation errors. An error analysis of any particular program is about as complex as the problem which is being solved by the program. Consequently, except for unusual cases, an analysis of error is not made. An estimate of the accuracy of the program can be found from check cases for which the answer is already known. Error is reduced by scaling the program so that all potentiometer values and amplifier gains are reasonable. Frequently, in the process of scaling a problem, it will be found that some parts of the model are not significant and can be eliminated. Scaling is a good check on reasonability.